# ardware Manua

# R8C/14 Group, R8C/15 Group

Hardware Manual

RENESAS 16-BIT SINGLE-CHIP MICROCOMPUTER

M16C FAMILY / R8C/Tiny SERIES

All information contained in these materials, including products and product specifications, represents information on the product at the time of publication and is subject to change by Renesas Technology Corp. without notice. Please review the latest information published by Renesas Technology Corp. through various means, including the Renesas Technology Corp. website (http://www.renesas.com).

Rev.2.10 Revision Date:Jan 19, 2006

# Keep safety first in your circuit designs!

1. Renesas Technology Corp. puts the maximum effort into making semiconductor products better and more reliable, but there is always the possibility that trouble may occur with them. Trouble with semiconductors may lead to personal injury, fire or property damage. Remember to give due consideration to safety when making your circuit designs, with appropriate measures such as (i) placement of substitutive, auxiliary circuits, (ii) use of non-flammable material or (iii) prevention against any malfunction or mishap.

# Notes regarding these materials

- 1. These materials are intended as a reference to assist our customers in the selection of the Renesas Technology Corp. product best suited to the customer's application; they do not convey any license under any intellectual property rights, or any other rights, belonging to Renesas Technology Corp. or a third party.

- 2. Renesas Technology Corp. assumes no responsibility for any damage, or infringement of any third-party's rights, originating in the use of any product data, diagrams, charts, programs, algorithms, or circuit application examples contained in these materials.

- 3. All information contained in these materials, including product data, diagrams, charts, programs and algorithms represents information on products at the time of publication of these materials, and are subject to change by Renesas Technology Corp. without notice due to product improvements or other reasons. It is therefore recommended that customers contact Renesas Technology Corp. or an authorized Renesas Technology Corp. product distributor for the latest product information before purchasing a product listed herein.

- The information described here may contain technical inaccuracies or typographical errors. Renesas Technology Corp. assumes no responsibility for any damage, liability, or other loss rising from these inaccuracies or errors.

- Please also pay attention to information published by Renesas Technology Corp. by various means, including the Renesas Technology Corp. Semiconductor home page (http://www.renesas.com).

- 4. When using any or all of the information contained in these materials, including product data, diagrams, charts, programs, and algorithms, please be sure to evaluate all information as a total system before making a final decision on the applicability of the information and products. Renesas Technology Corp. assumes no responsibility for any damage, liability or other loss resulting from the information contained herein.

- 5. Renesas Technology Corp. semiconductors are not designed or manufactured for use in a device or system that is used under circumstances in which human life is potentially at stake. Please contact Renesas Technology Corp. or an authorized Renesas Technology Corp. product distributor when considering the use of a product contained herein for any specific purposes, such as apparatus or systems for transportation, vehicular, medical, aerospace, nuclear, or undersea repeater use.

- 6. The prior written approval of Renesas Technology Corp. is necessary to reprint or reproduce in whole or in part these materials.

- 7. If these products or technologies are subject to the Japanese export control restrictions, they must be exported under a license from the Japanese government and cannot be imported into a country other than the approved destination.

- Any diversion or reexport contrary to the export control laws and regulations of Japan and/ or the country of destination is prohibited.

- 8. Please contact Renesas Technology Corp. for further details on these materials or the products contained therein.

# How to Use This Manual

# 1. Introduction

This hardware manual provides detailed information on the R8C/14 Group, R8C/15 Group of microcomputers.

Users are expected to have basic knowledge of electric circuits, logical circuits and microcomputers.

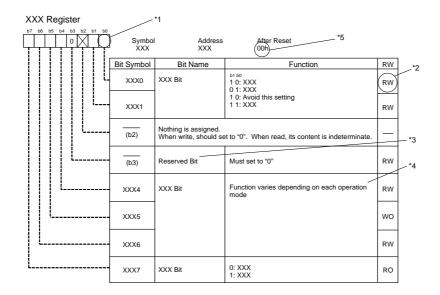

# 2. Register Diagram

The symbols, and descriptions, used for bit function in each register are shown below.

\*1

Blank:Set to "0" or "1" according to the application

- 0: Set to "0"

- 1: Set to "1"

- X: Nothing is assigned

\*2

RW: Read and write

RO: Read only

WO: Write only

-: Nothing is assigned

\*3

•Reserved bit

Reserved bit. Set to specified value.

\*1

Nothing is assigned

Nothing is assigned to the bit concerned. As the bit may be use for future functions, set to "0" when writing to this bit.

•Do not set to this value

The operation is not guaranteed when a value is set.

•Function varies depending on mode of operation

Bit function varies depending on peripheral function mode.

Refer to respective register for each mode.

\*5

Follow the text in each manual for binary and hexadecimal notations.

# 3. M16C Family Documents

The following documents were prepared for the M16C family.(1)

| Document                 | Contents                                                                                                                                                                                       |  |

|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Short Sheet              | Hardware overview                                                                                                                                                                              |  |

| Data Sheet               | Hardware overview and electrical characteristics                                                                                                                                               |  |

| Hardware Manual          | Hardware specifications (pin assignments, memory maps, periphe specifications, electrical characteristics, timing charts).  *Refer to the application note for how to use peripheral functions |  |

| Software Manual          | Detailed description of assembly instructions and microcomputer performance of each instruction                                                                                                |  |

| Application Note         | Usage and application examples of peripheral functions     Sample programs     Introduction to the basic functions in the M16C family     Programming method with Assembly and C languages     |  |

| RENESAS TECHNICAL UPDATE | Preliminary report about the specification of a product, a document, etc.                                                                                                                      |  |

# NOTES:

1. Before using this material, please visit the our website to verify that this is the most updated document available.

# **Table of Contents**

| SI | FR Pa | ige Reference                                   | B - 1         |

|----|-------|-------------------------------------------------|---------------|

| 1. | Ove   | erview                                          | 1             |

|    | 1.1   | Applications                                    | 1             |

|    | 1.2   | Performance Overview                            | 2             |

|    | 1.3   | Block Diagram                                   | 4             |

|    | 1.4   | Product Information                             | 5             |

|    | 1.5   | Pin Assignments                                 | 7             |

|    | 1.6   | Pin Description                                 | 8             |

| 2. | Cer   | ntral Processing Unit (CPU)                     | 10            |

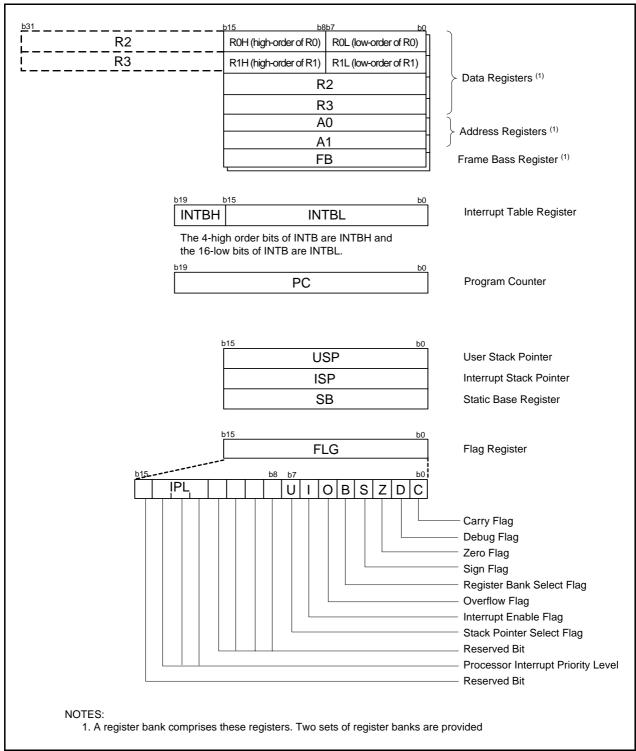

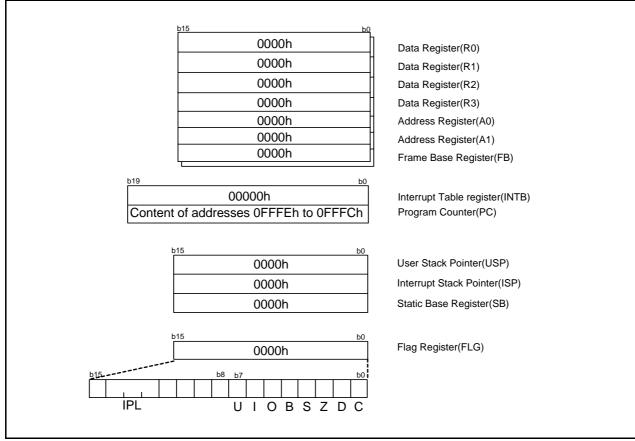

|    | 2.1   | Data Registers (R0, R1, R2 and R3)              | 11            |

|    | 2.2   | Address Registers (A0 and A1)                   | 11            |

|    | 2.3   | Frame Base Register (FB)                        | 11            |

|    | 2.4   | Interrupt Table Register (INTB)                 | 11            |

|    | 2.5   | Program Counter (PC)                            | 11            |

|    | 2.6   | User Stack Pointer (USP) and Interrupt Stack Po | inter (ISP)11 |

|    | 2.7   | Static Base Register (SB)                       | 11            |

|    | 2.8   | Flag Register (FLG)                             | 11            |

|    | 2.8   | .1 Carry Flag (C)                               | 11            |

|    | 2.8   | .2 Debug Flag (D)                               | 11            |

|    | 2.8   | .3 Zero Flag (Z)                                | 11            |

|    | 2.8   | .4 Sign Flag (S)                                | 11            |

|    | 2.8   | .5 Register Bank Select Flag (B)                | 11            |

|    | 2.8   | .6 Overflow Flag (O)                            | 11            |

|    | 2.8   | .7 Interrupt Enable Flag (I Flag)               | 12            |

|    | 2.8   | .8 Stack Pointer Select Flag (U Flag)           | 12            |

|    | 2.8   | .9 Processor Interrupt Priority Level (IPL)     | 12            |

|    | 2.8   | .10 Reserved Bit                                | 12            |

| 3. | Ме    | mory                                            | 13            |

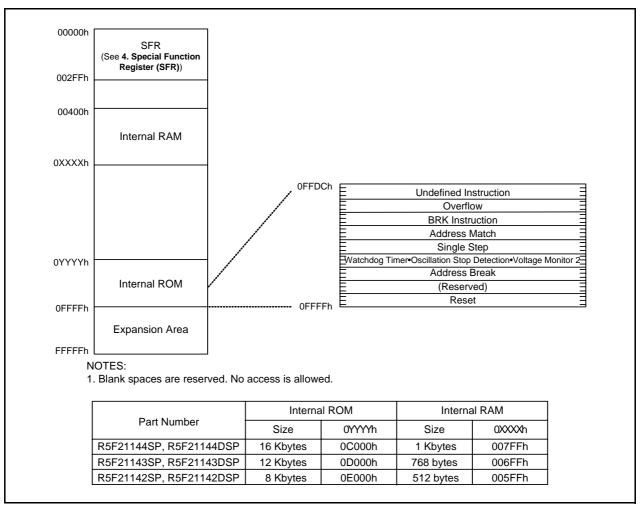

|    | 3.1   | R8C/14 Group                                    | 13            |

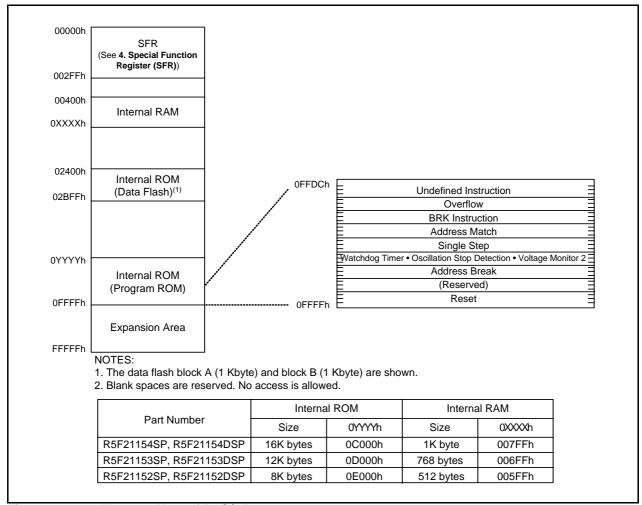

|    | 3.2   | R8C/15 Group                                    | 14            |

| 4. | Spe  | cial Function Register (SFR)                            | 15 |

|----|------|---------------------------------------------------------|----|

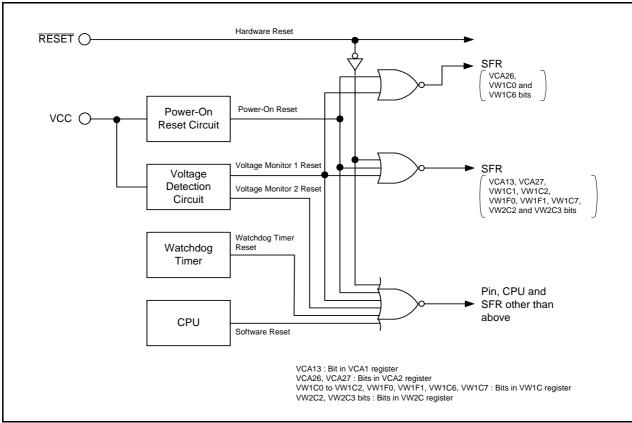

| 5. | Res  | set                                                     | 19 |

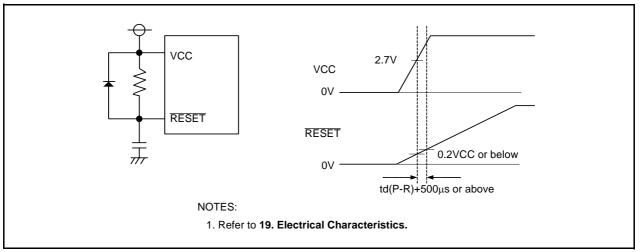

|    | 5.1  | Hardware Reset                                          | 21 |

|    | 5.1. | 1 When the power supply is stable                       | 21 |

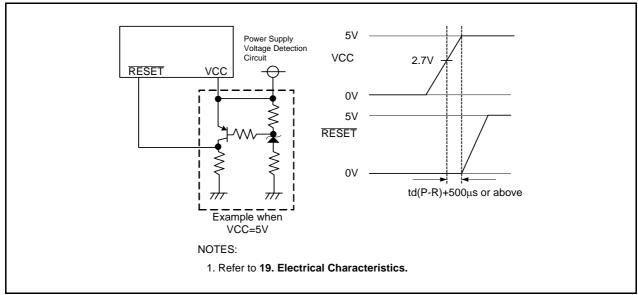

|    | 5.1. | 2 Power on                                              | 21 |

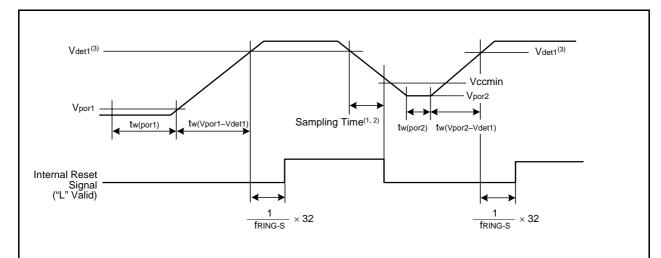

|    | 5.2  | Power-On Reset Function                                 | 23 |

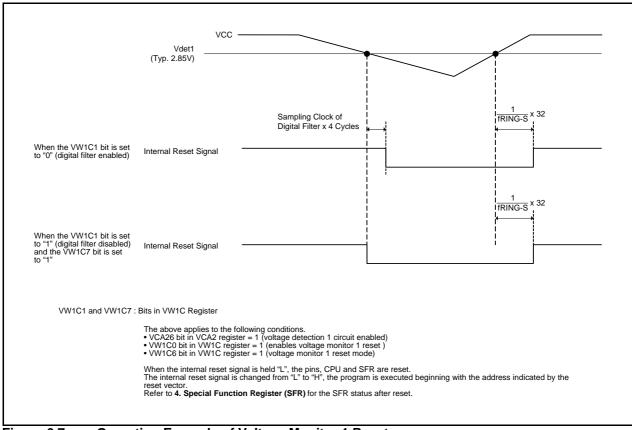

|    | 5.3  | Voltage Monitor 1 Reset                                 | 24 |

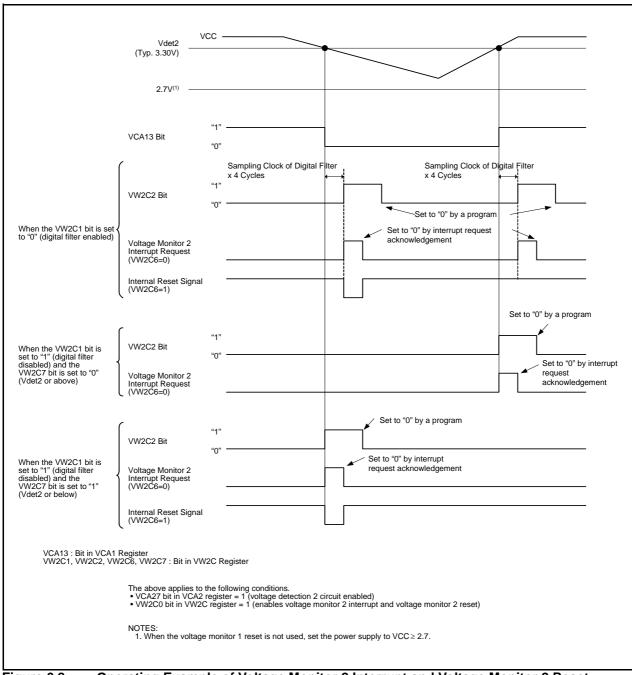

|    | 5.4  | Voltage Monitor 2 Reset                                 | 24 |

|    | 5.5  | Watchdog Timer Reset                                    | 24 |

|    | 5.6  | Software Reset                                          | 24 |

| 6. | Volt | age Detection Circuit                                   | 25 |

|    | 6.1  | Monitoring VCC Input Voltage                            | 31 |

|    | 6.1. | 1 Monitoring Vdet1                                      | 31 |

|    | 6.1. | 2 Monitoring Vdet2                                      | 31 |

|    | 6.2  | Voltage Monitor 1 Reset                                 | 32 |

|    | 6.3  | Voltage Monitor 2 Interrupt and Voltage Monitor 2 Reset | 33 |

| 7. | Pro  | cessor Mode                                             | 35 |

|    | 7.1  | Types of Processor Mode                                 | 35 |

| 8. | Bus  |                                                         | 37 |

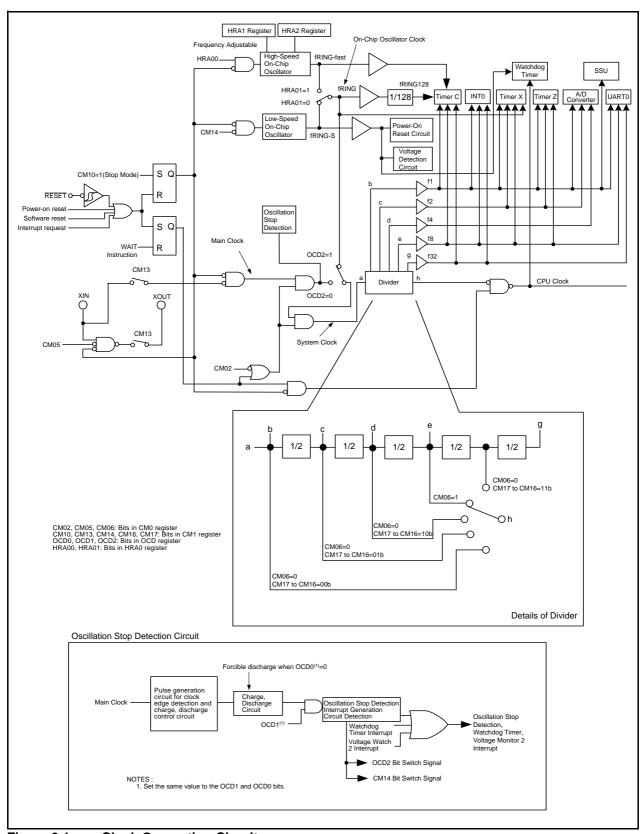

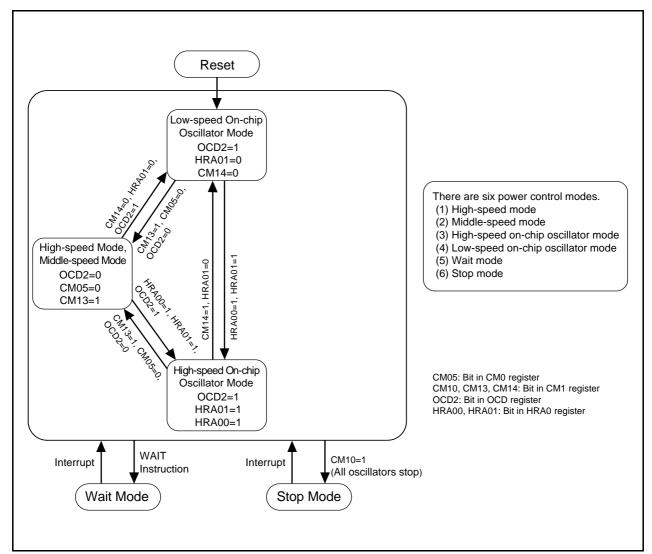

| 9. | Clo  | ck Generation Circuit                                   | 38 |

|    | 9.1  | Main Clock                                              | 45 |

|    | 9.2  | On-Chip Oscillator Clock                                | 46 |

|    | 9.2. | 1 Low-Speed On-Chip Oscillator Clock                    | 46 |

|    | 9.2. | 2 High-Speed On-Chip Oscillator Clock                   | 46 |

|    | 9.3  | CPU Clock and Peripheral Function Clock                 | 47 |

|    | 9.3. | 1 System Clock                                          | 47 |

|    | 9.3. | 2 CPU Clock                                             | 47 |

|    | 9.3. | 3 Peripheral Function Clock (f1, f2, f4, f8, f32)       | 47 |

|    | 9.3. | 4 fRING and fRING128                                    | 47 |

|    | 9.3. | 5 fRING-fast                                            | 47 |

|    | 9.3. | 6 fRING-S                                               | 47 |

|    | 94   | Power Control                                           | 48 |

|     | 9.4.1    | Normal Operating Mode                          | 48  |

|-----|----------|------------------------------------------------|-----|

|     | 9.4.2    | Wait Mode                                      | 49  |

|     | 9.4.3    | Stop Mode                                      | 51  |

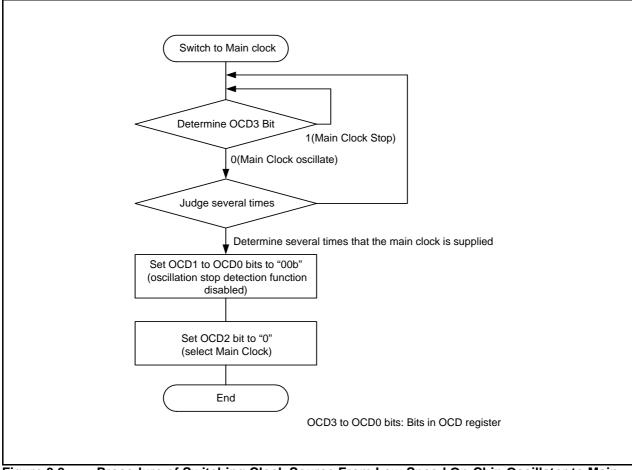

| 9.  | .5 Os    | cillation Stop Detection Function              | 53  |

|     | 9.5.1    | How to Use Oscillation Stop Detection Function | 53  |

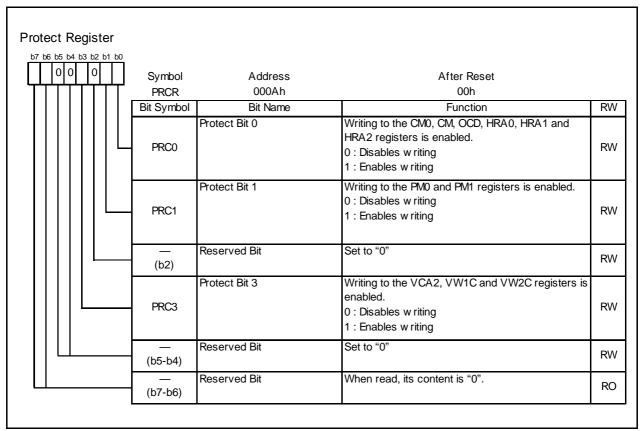

| 10. | Protect  | ion                                            | 55  |

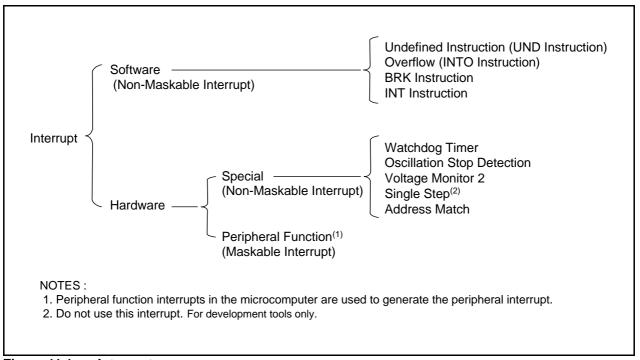

| 11. | Interrup | ot                                             | 56  |

| 1   | 1.1 Inte | errupt Overview                                | 56  |

|     | 11.1.1   | Types of Interrupts                            | 56  |

|     | 11.1.2   | Software Interrupts                            | 57  |

|     | 11.1.3   | Special Interrupts                             | 58  |

|     | 11.1.4   | Peripheral Function Interrupt                  | 58  |

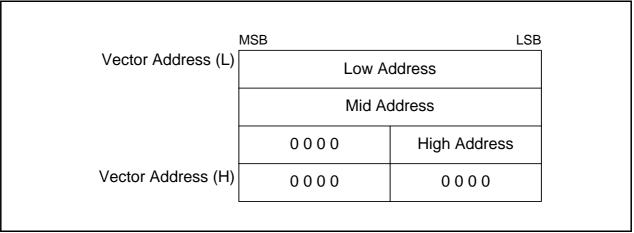

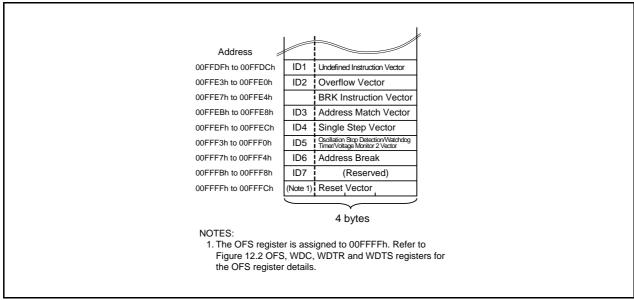

|     | 11.1.5   | Interrupts and Interrupt Vector                | 59  |

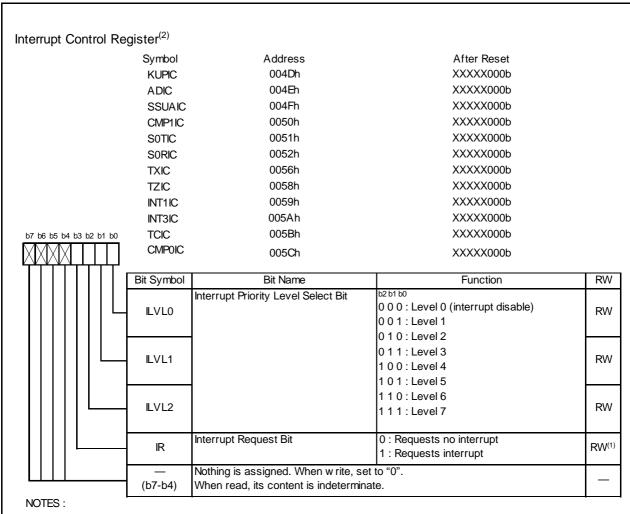

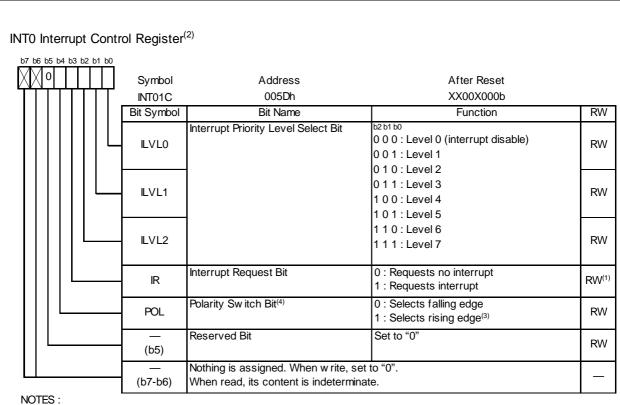

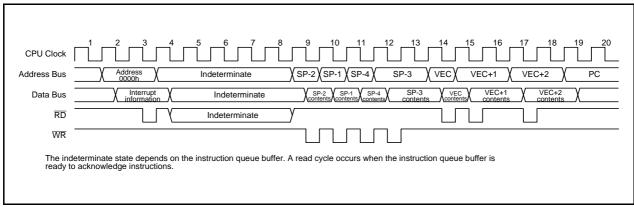

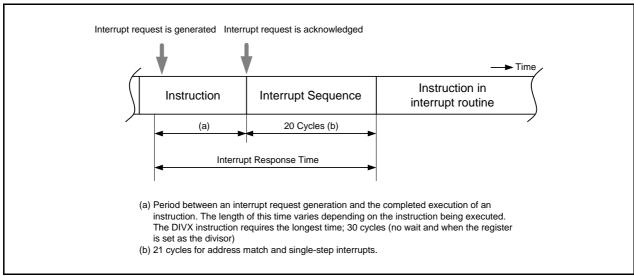

|     | 11.1.6   | Interrupt Control                              | 61  |

| 1   | 1.2 ĪN7  | Interrupt                                      | 69  |

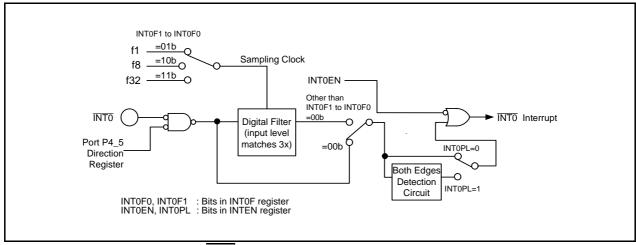

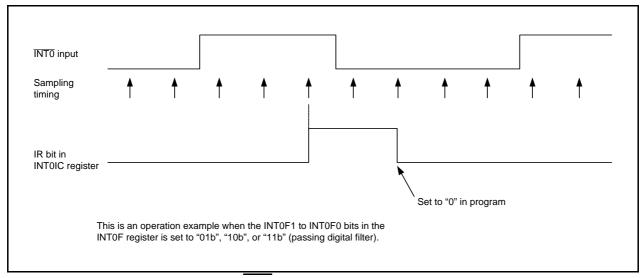

|     | 11.2.1   | INTO Interrupt                                 | 69  |

|     | 11.2.2   | INTO Input Filter                              | 70  |

|     | 11.2.3   | INT1 Interrupt                                 | 71  |

|     | 11.2.4   | INT3 Interrupt                                 | 72  |

| 1   | 1.3 Ke   | y Input Interrupt                              | 74  |

| 1   | 1.4 Ad   | dress Match Interrupt                          | 76  |

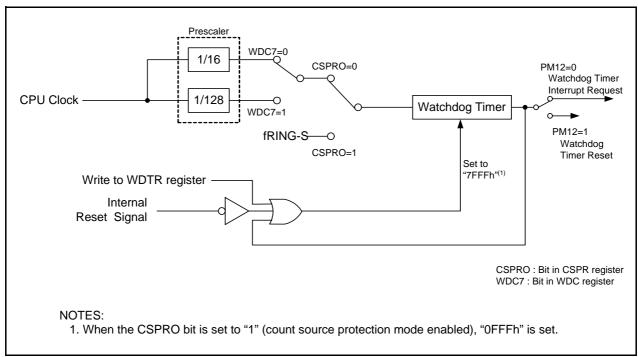

| 12. | Watcho   | dog Timer                                      | 78  |

| 1:  | 2.1 Wh   | nen Count Source Protection Mode Disabled      | 81  |

| 1:  | 2.2 Wh   | nen Count Source Protection Mode Enabled       | 82  |

| 13. | Timers   |                                                | 83  |

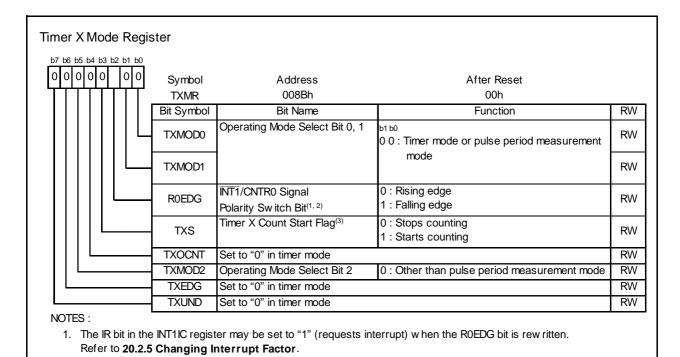

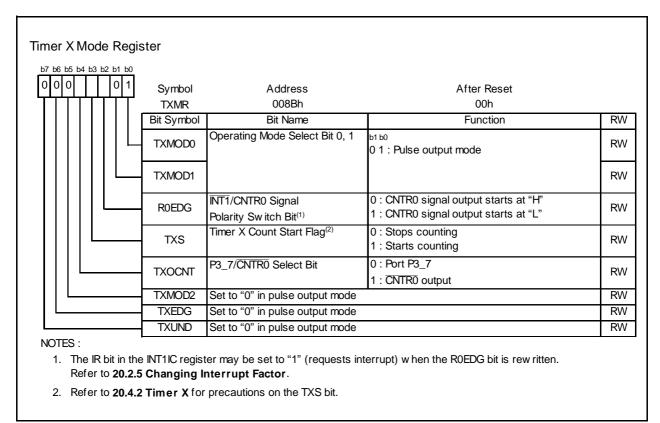

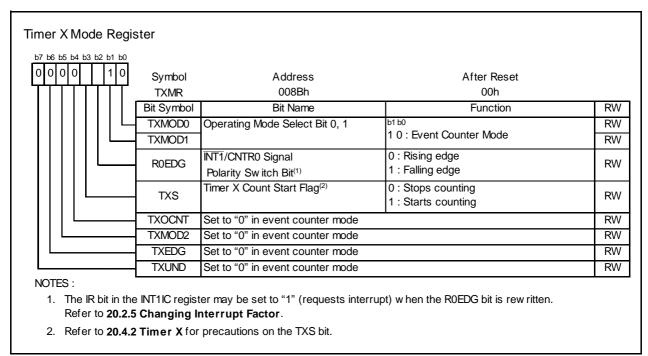

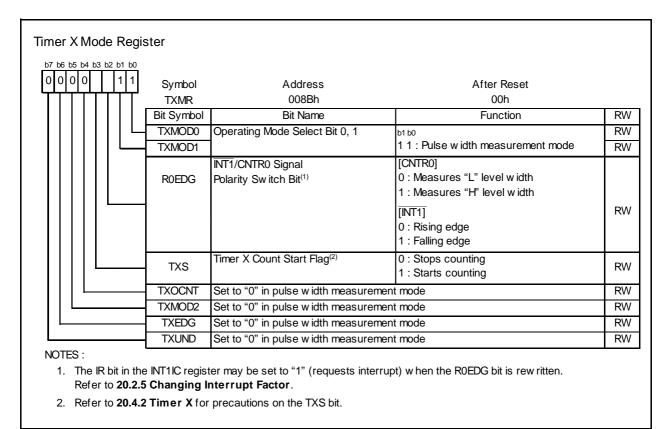

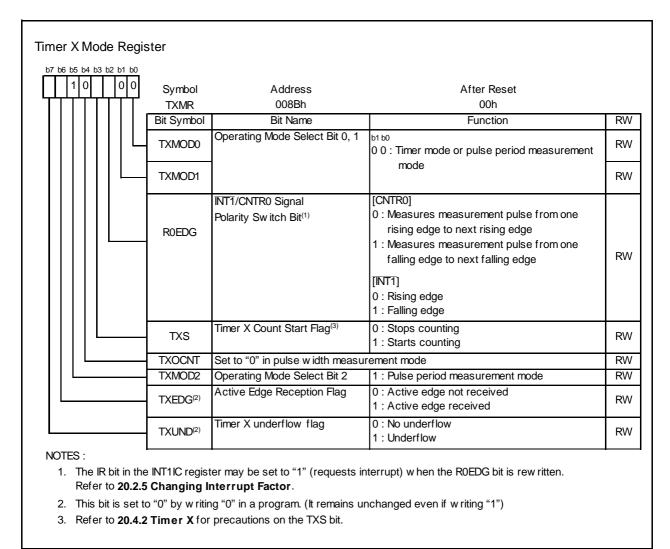

| 1:  | 3.1 Tin  | ner X                                          | 84  |

|     | 13.1.1   | Timer Mode                                     | 87  |

|     | 13.1.2   | Pulse Output Mode                              | 88  |

|     | 13.1.3   | Event Counter Mode                             | 90  |

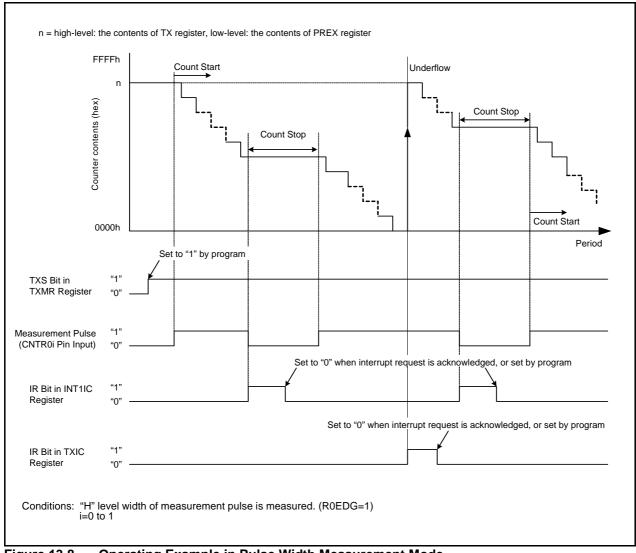

|     | 13.1.4   | Pulse Width Measurement Mode                   | 92  |

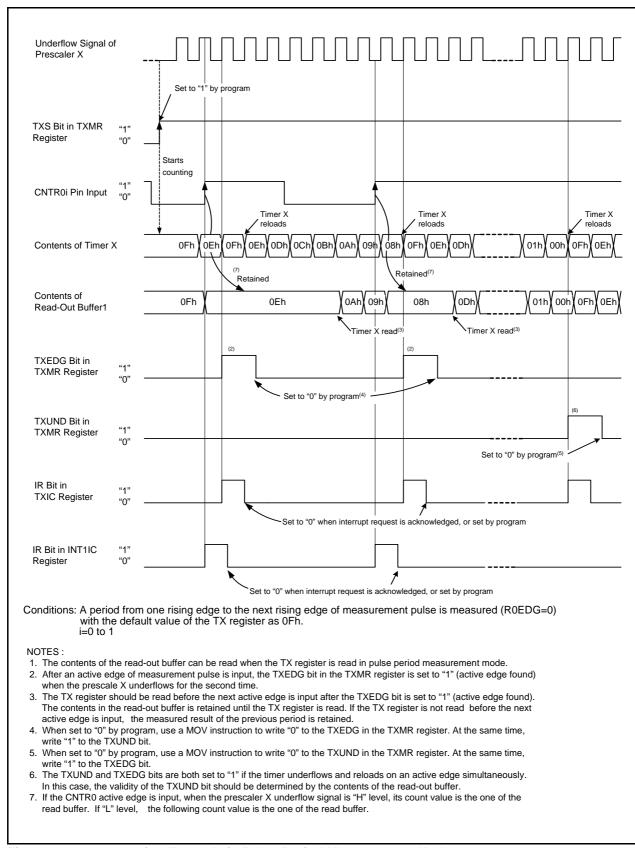

|     | 13.1.5   | Pulse Period Measurement Mode                  | 95  |

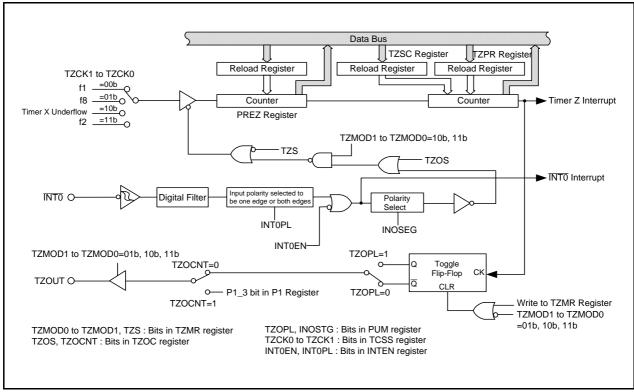

| 1:  | 3.2 Tin  | ner Z                                          | 98  |

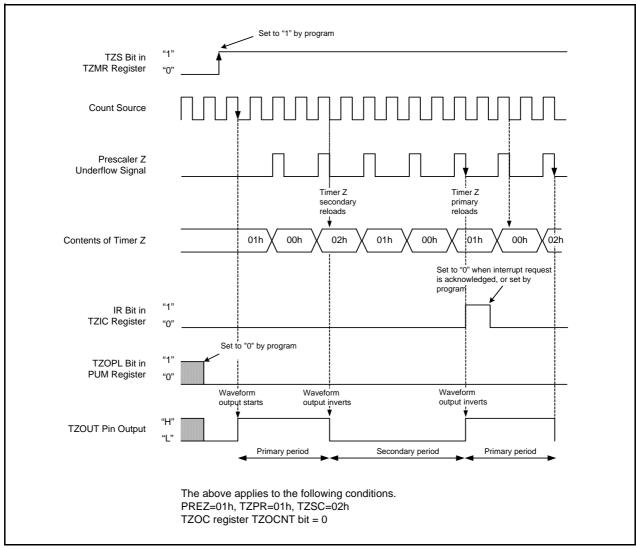

|     | 13.2.1   | Timer Mode                                     | 103 |

|     | 13. | 2.2   | Programmable Waveform Generation Mode                       | 105 |

|-----|-----|-------|-------------------------------------------------------------|-----|

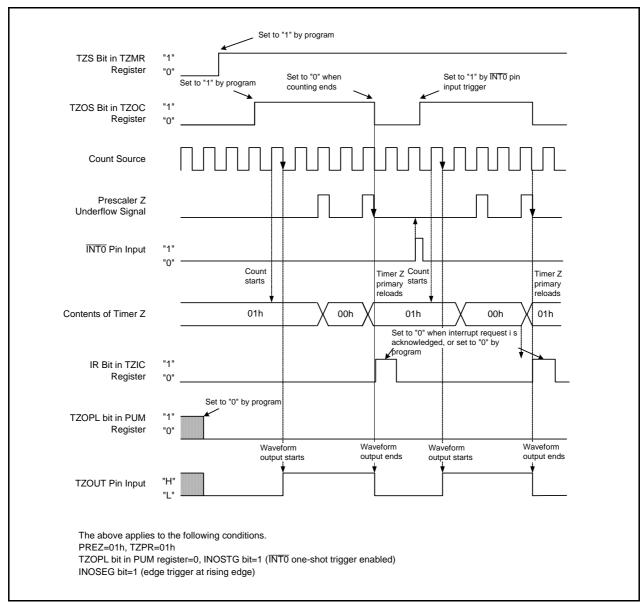

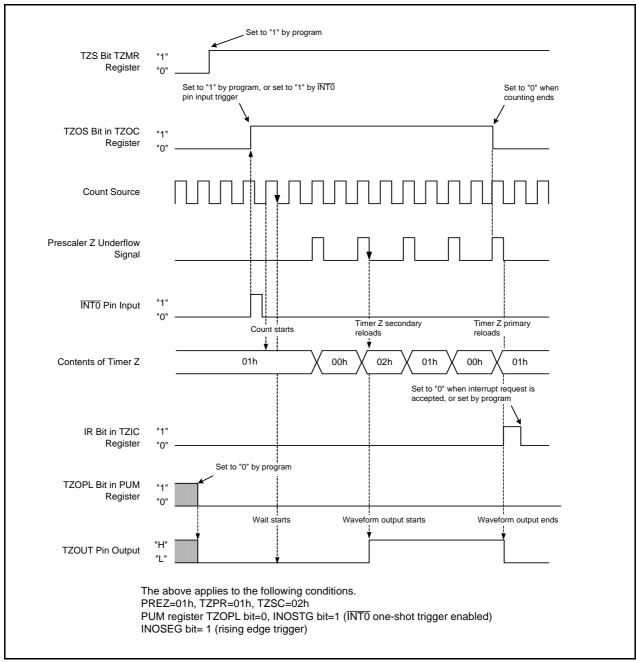

|     | 13. | 2.3   | Programmable One-shot Generation Mode                       | 108 |

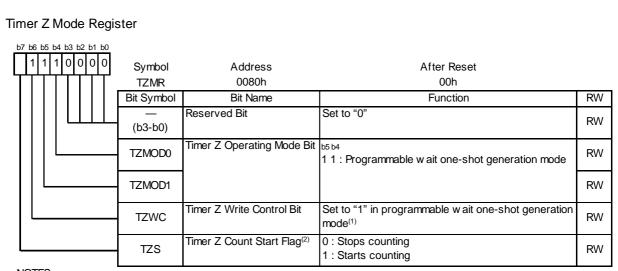

|     | 13. | 2.4   | Programmable Wait One-shot Generation Mode                  | 111 |

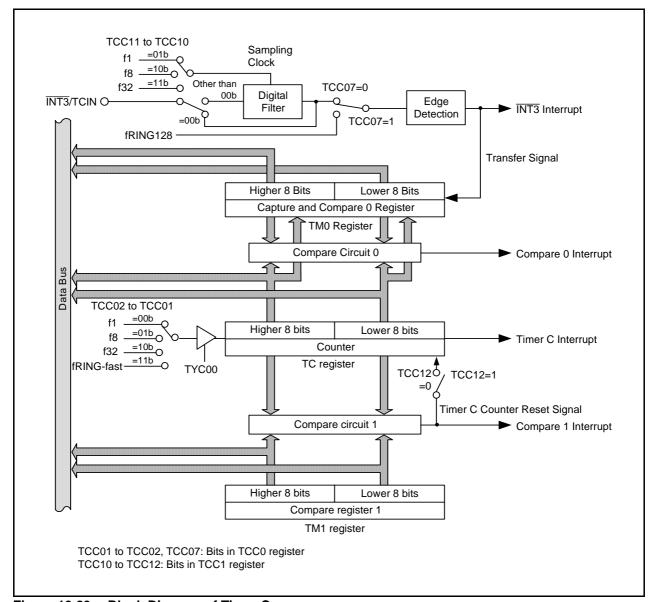

| 1   | 3.3 | Tin   | ner C                                                       | 115 |

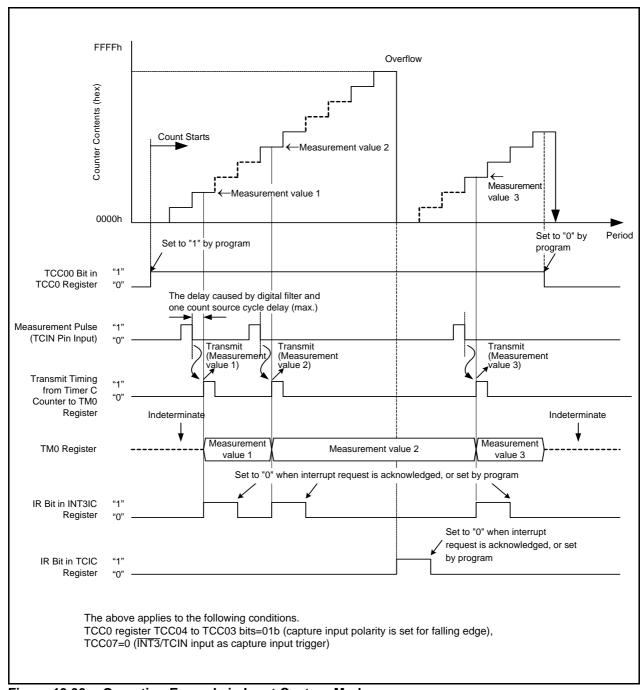

|     | 13. | 3.1   | Input Capture Mode                                          | 121 |

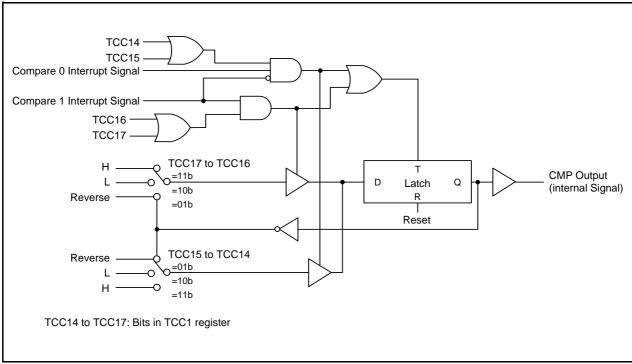

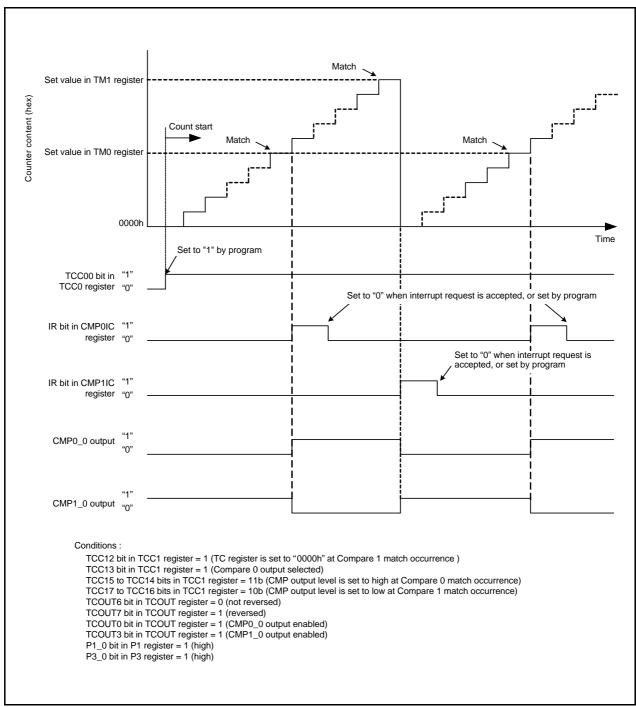

|     | 13. | 3.2   | Output Compare Mode                                         | 123 |

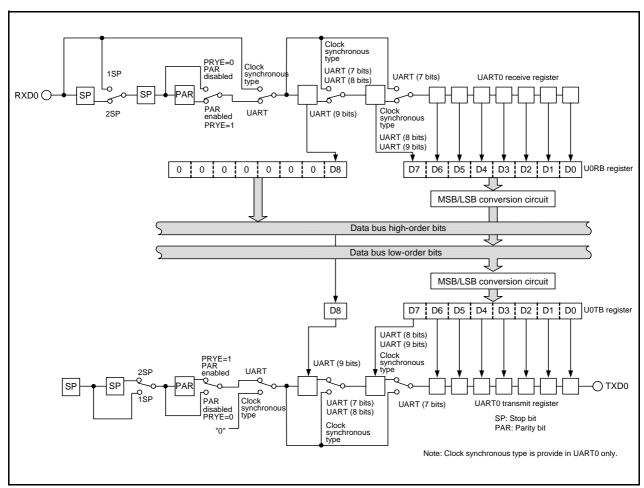

| 14. | Sei | ial I | nterface                                                    | 125 |

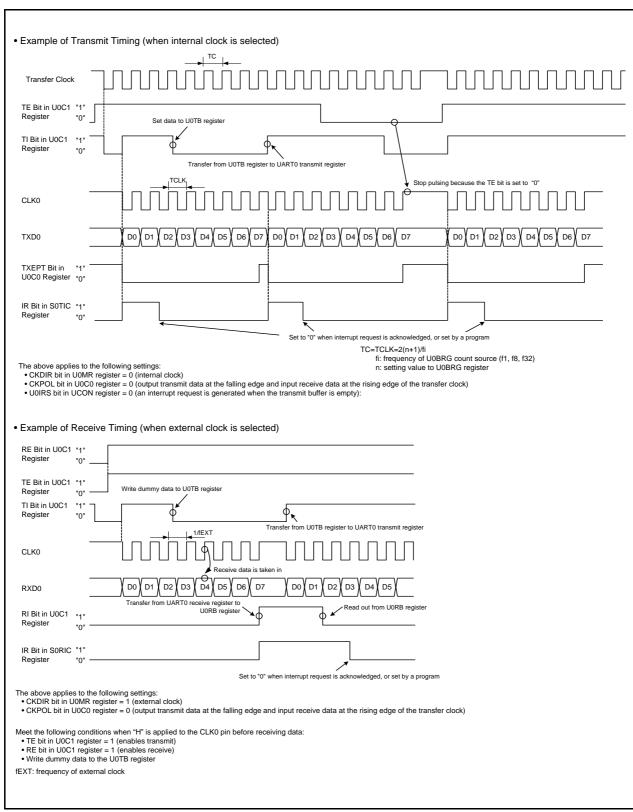

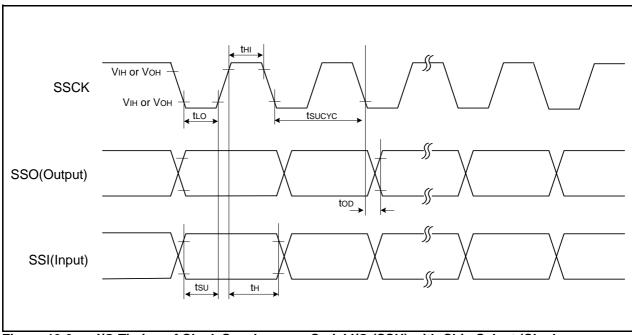

| 1   | 4.1 | Clo   | ck Synchronous Serial I/O Mode                              | 130 |

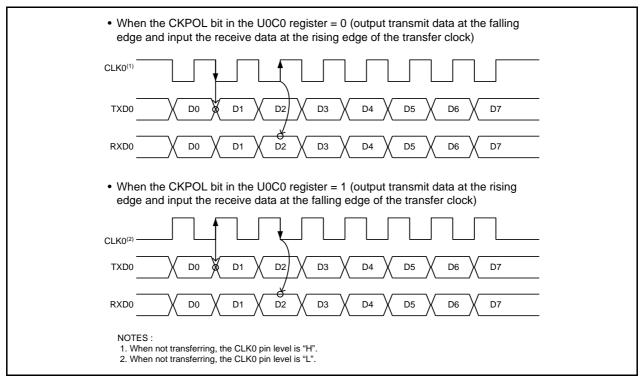

|     | 14. | 1.1   | Polarity Select Function                                    | 133 |

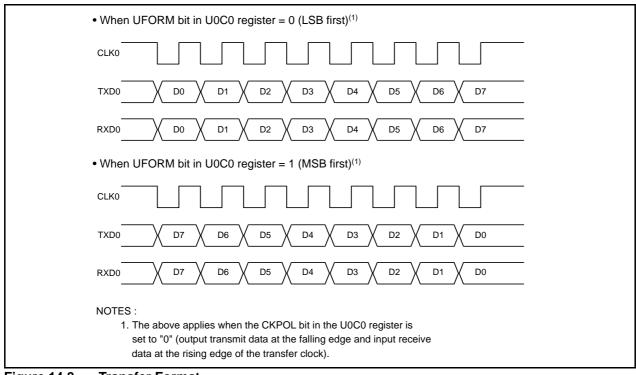

|     | 14. | 1.2   | LSB First/MSB First Select Function                         | 133 |

|     | 14. | 1.3   | Continuous Receive Mode                                     | 134 |

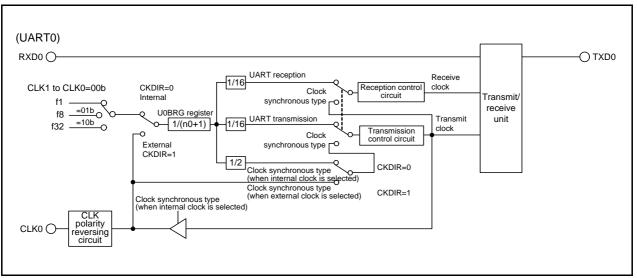

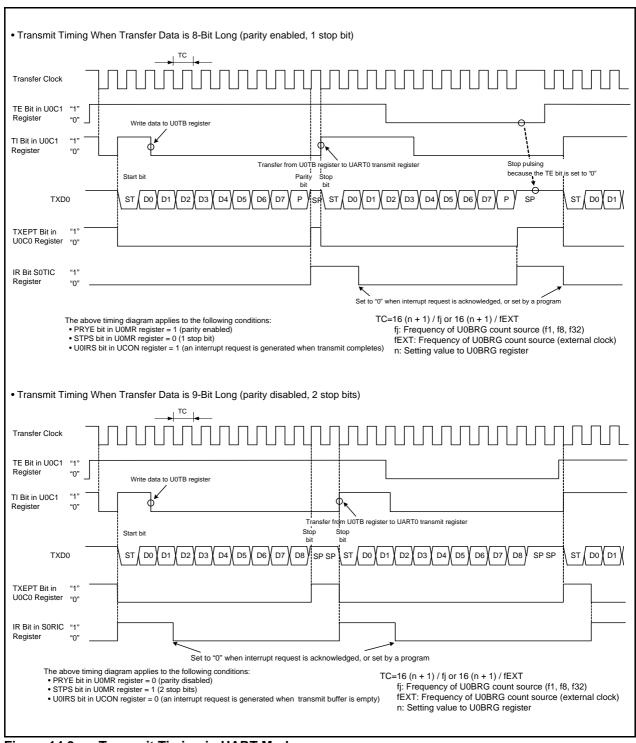

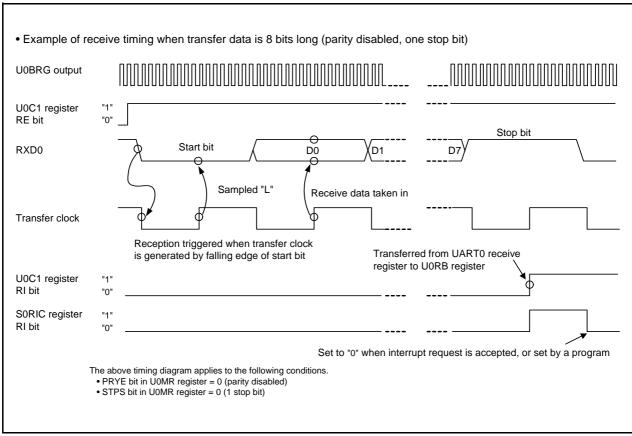

| 1   | 4.2 | Clo   | ck Asynchronous Serial I/O (UART) Mode                      | 135 |

|     | 14. | 2.1   | CNTR0 Pin Select Function                                   | 138 |

|     | 14. | 2.2   | Bit Rate                                                    | 139 |

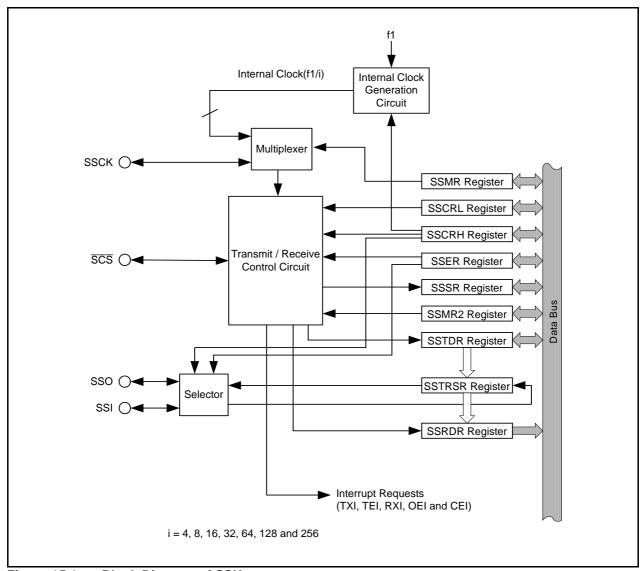

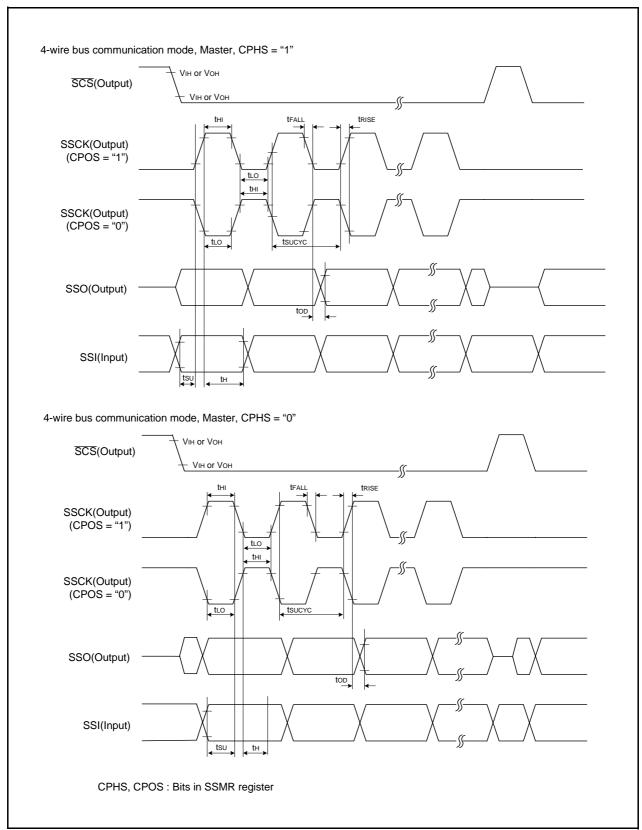

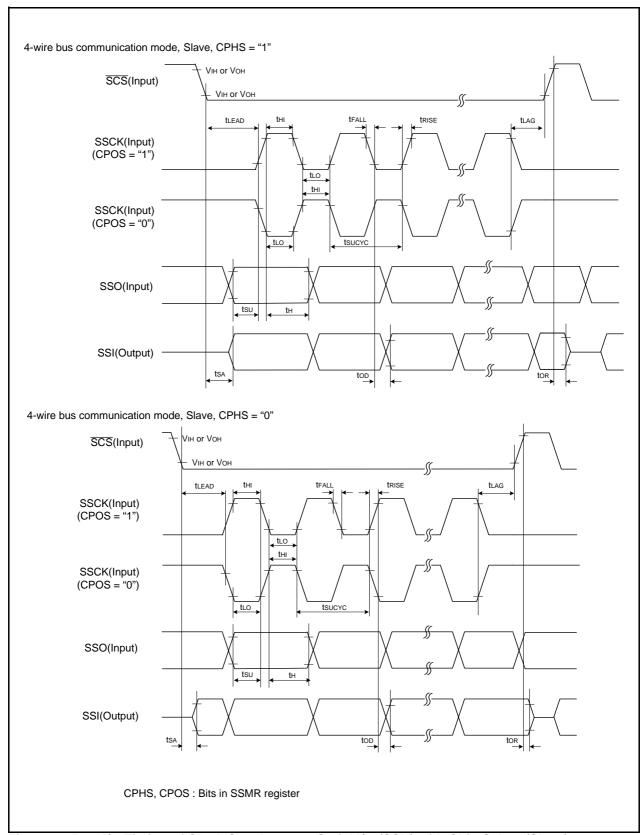

| 15. | Clo | ck S  | Synchronous Serial I/O with Chip Select (SSU)               | 140 |

| 1   | 5.1 | Tra   | nsfer Clock                                                 | 149 |

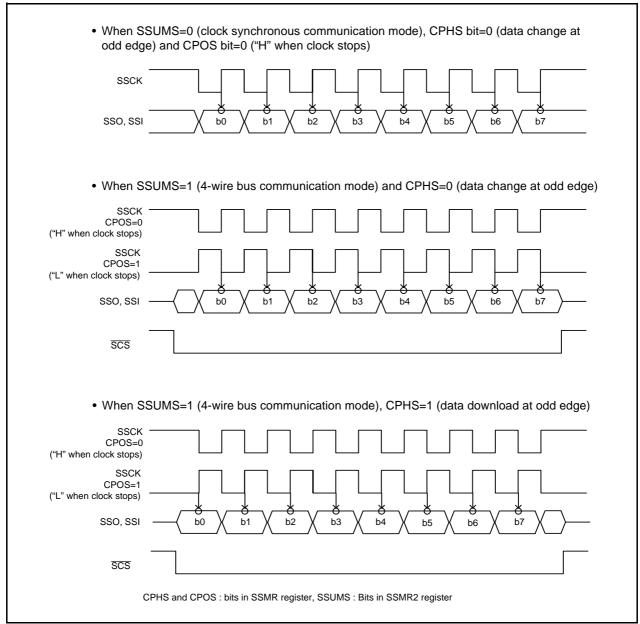

|     | 15. | 1.1   | Association between Transfer Clock Polarity, Phase and Data | 149 |

| 1   | 5.2 | SS    | Shift Register (SSTRSR)                                     | 151 |

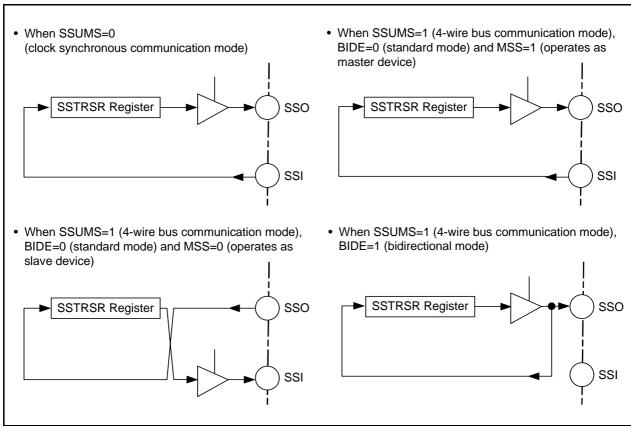

|     | 15. | 2.1   | Association between Data I/O Pin and SS Shift Register      | 151 |

| 1   | 5.3 | Inte  | errupt Requests                                             | 152 |

| 1   | 5.4 | Co    | mmunication Modes and Pin Functions                         | 153 |

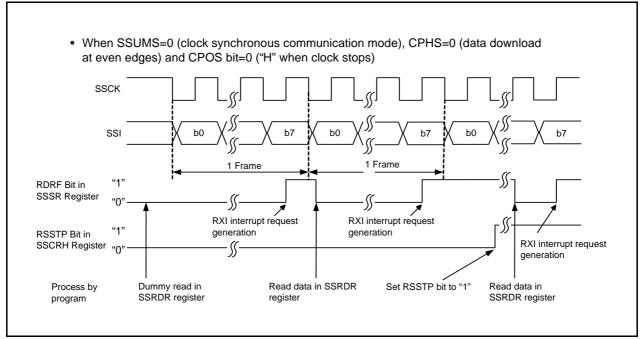

| 1   | 5.5 | Clo   | ck Synchronous Communication Mode                           | 154 |

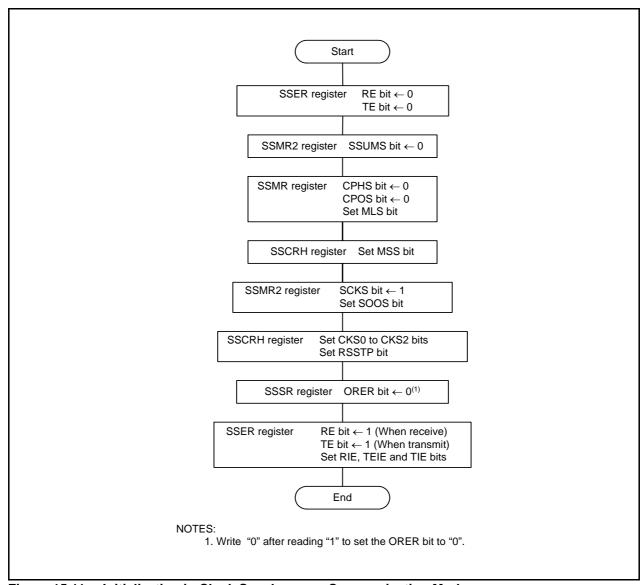

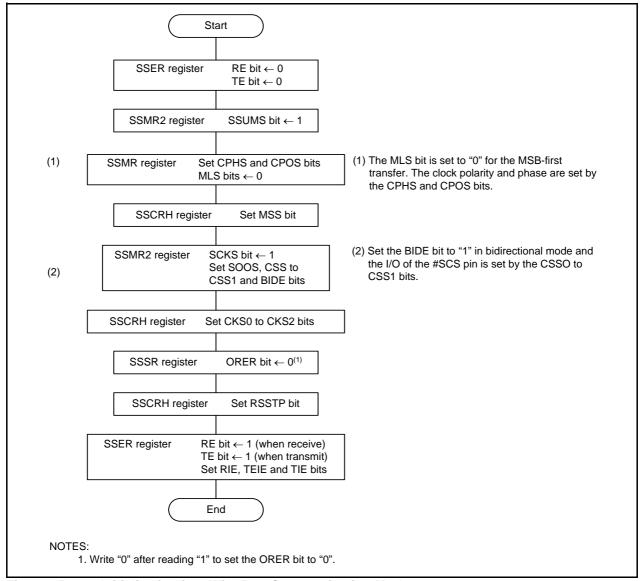

|     | 15. | 5.1   | Initialization in Clock Synchronous Communication Mode      | 154 |

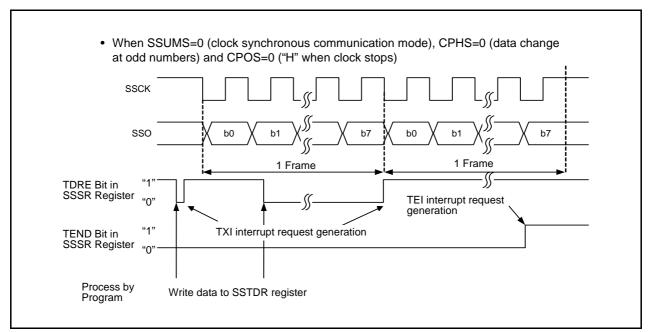

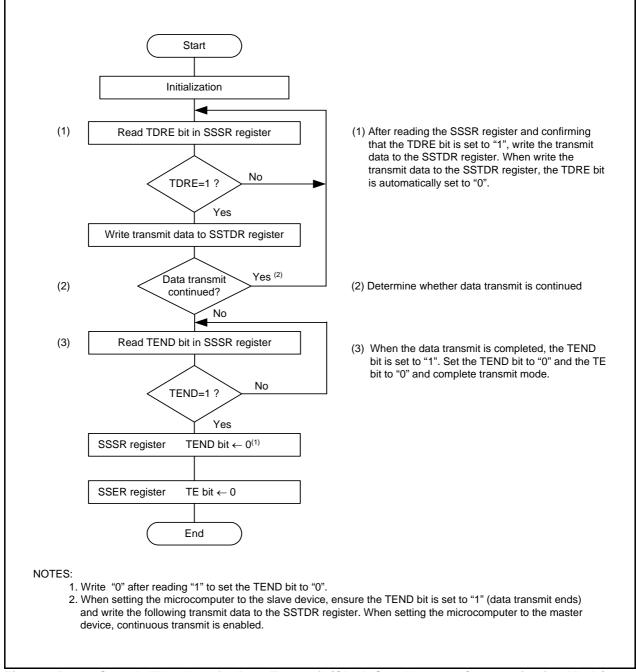

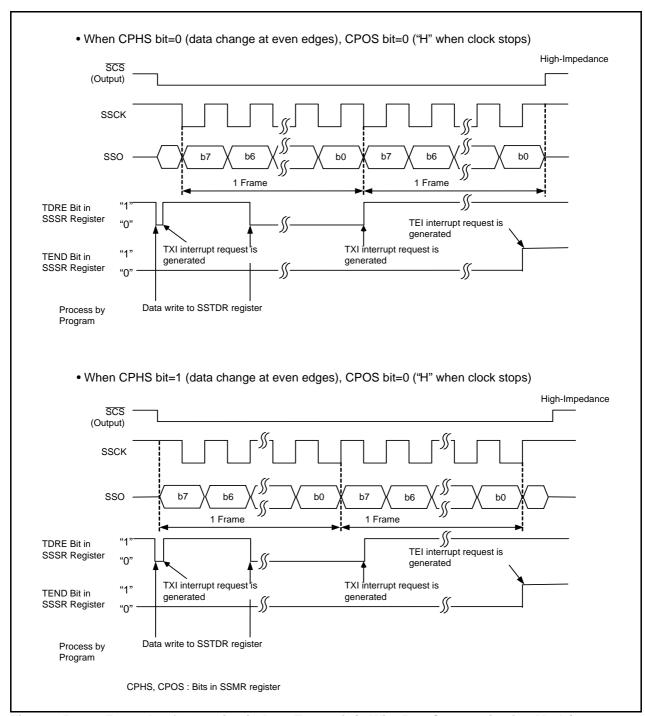

|     | 15. | 5.2   | Data Transmit                                               | 155 |

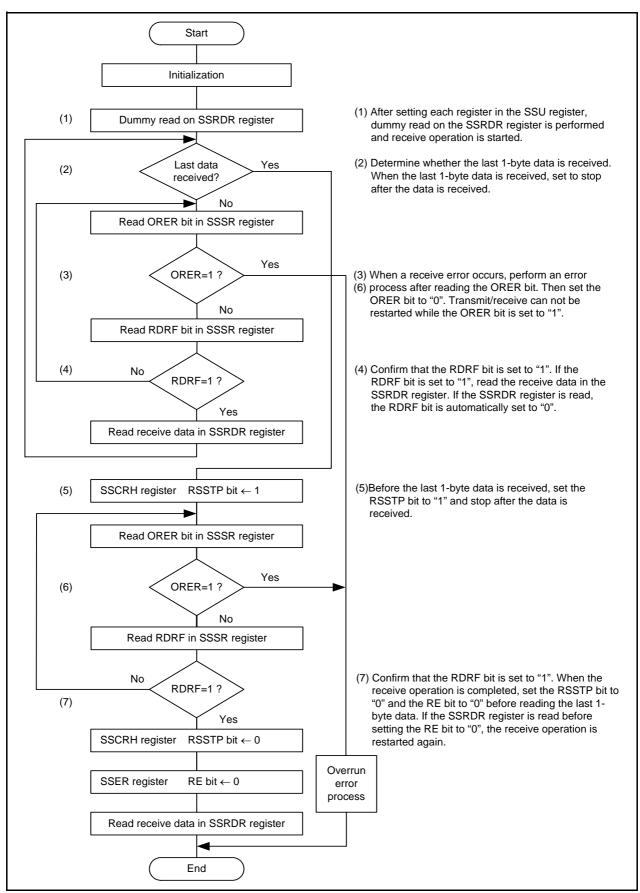

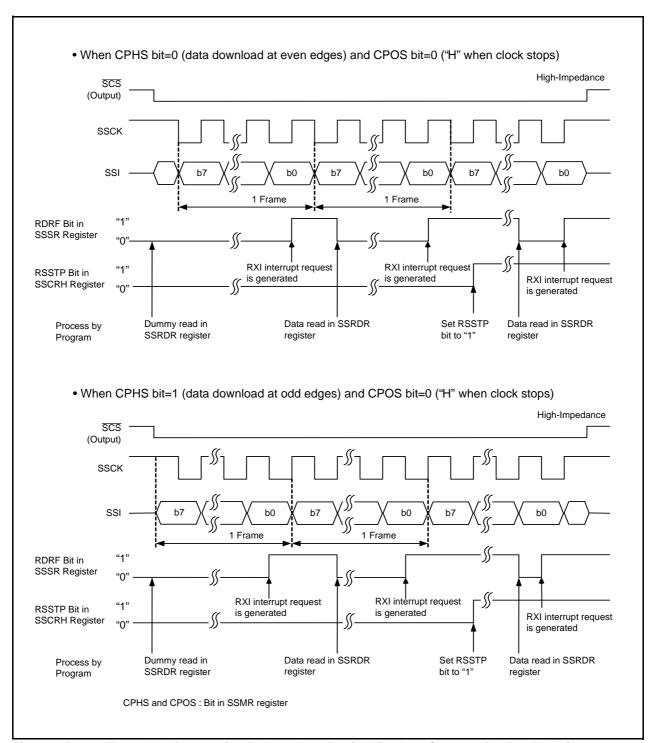

|     | 15. | 5.3   | Data Receive                                                | 157 |

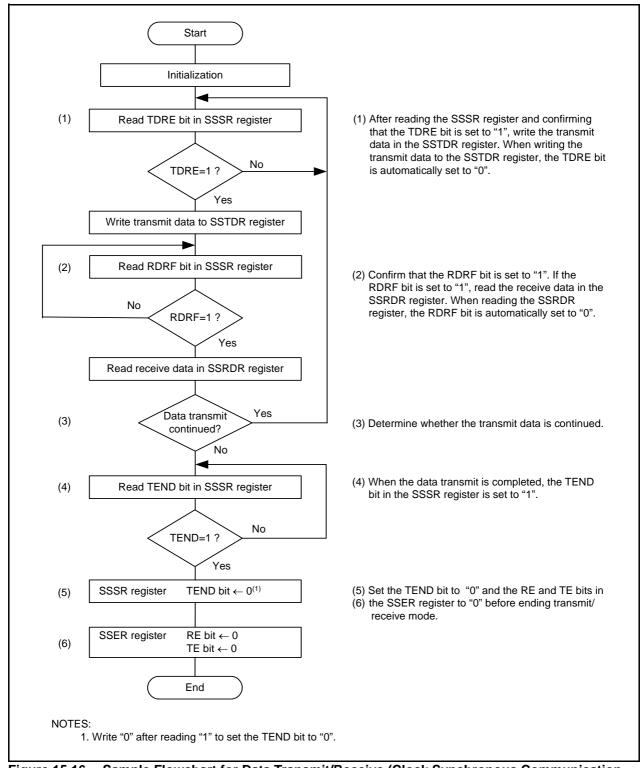

|     | 15. | 5.4   | Data Transmit/Receive                                       | 159 |

| 1   | 5.6 | Ор    | eration in 4-Wire Bus Communication Mode                    | 161 |

|     | 15. | 6.1   | Initialization in 4-Wire Bus Communication Mode             | 161 |

|     | 15. | 6.2   | Data Transmit                                               | 163 |

|     | 15. | 6.3   | Data Receive                                                | 165 |

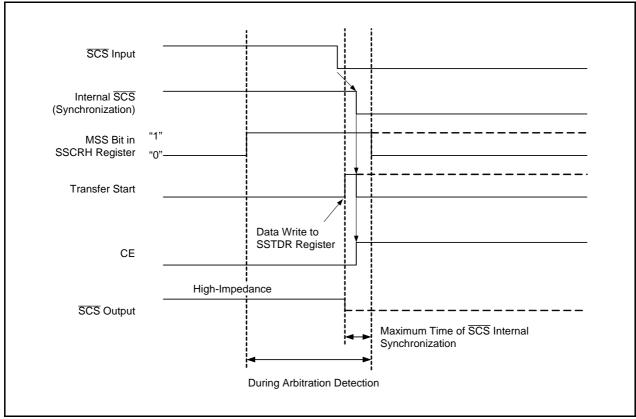

|     | 15. | 6.4   | SCS Pin Control and Arbitration                             | 167 |

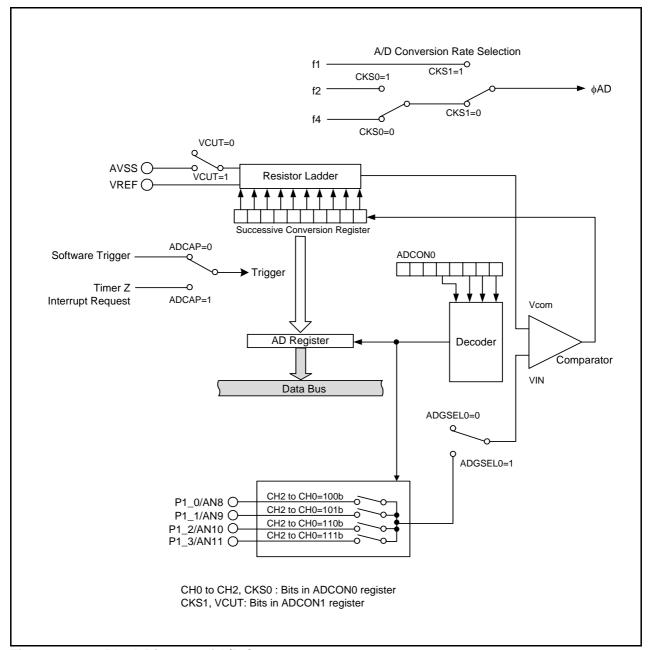

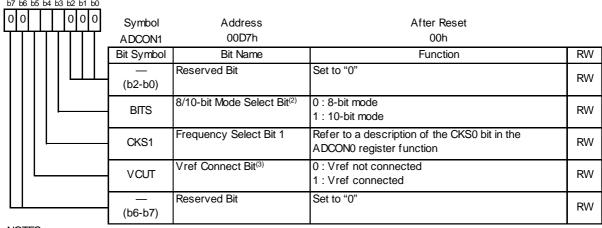

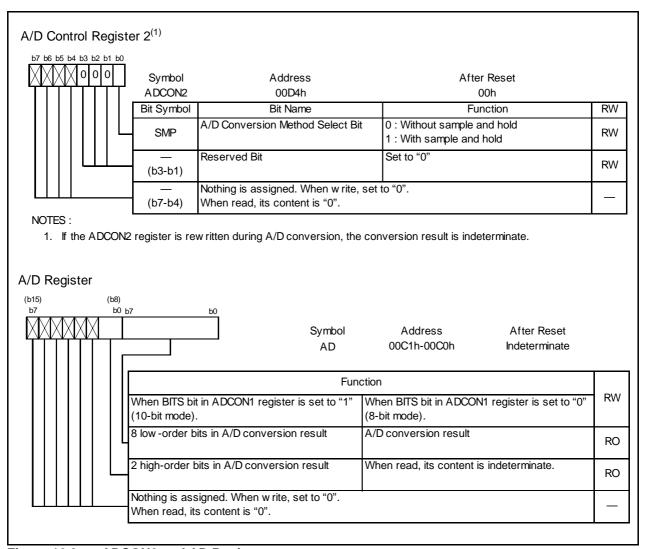

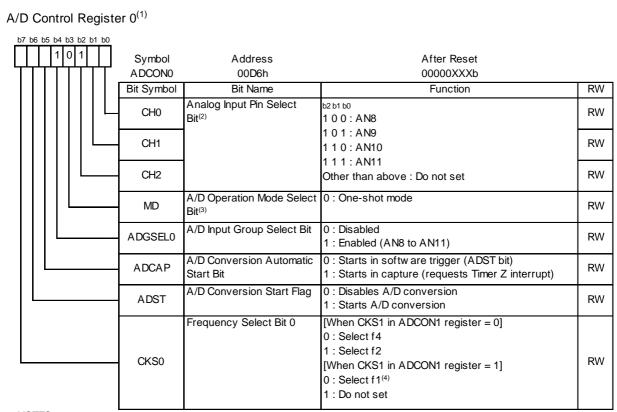

| 16. | A/D | ) Co  | nverter                                                     | 168 |

| 1   | 6 1 | On    | e-Shot Mode                                                 | 172 |

| 16  | 5.2  | Re    | peat Mode                                      | 174 |

|-----|------|-------|------------------------------------------------|-----|

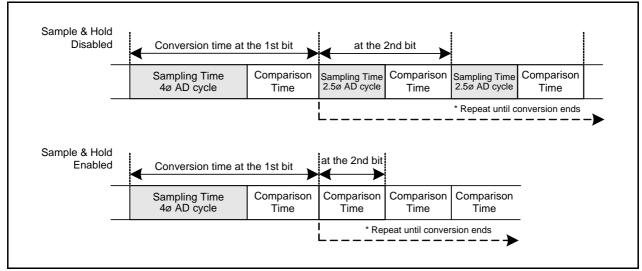

| 16  | 6.3  | Sa    | mple and Hold                                  | 176 |

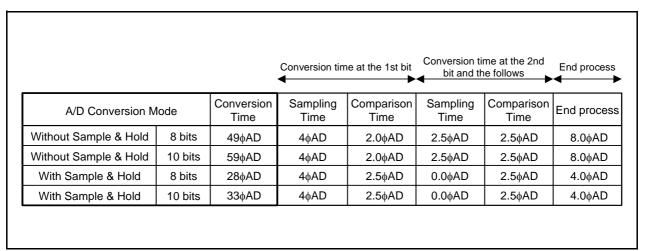

| 16  | 6.4  | A/E   | Conversion Cycles                              | 176 |

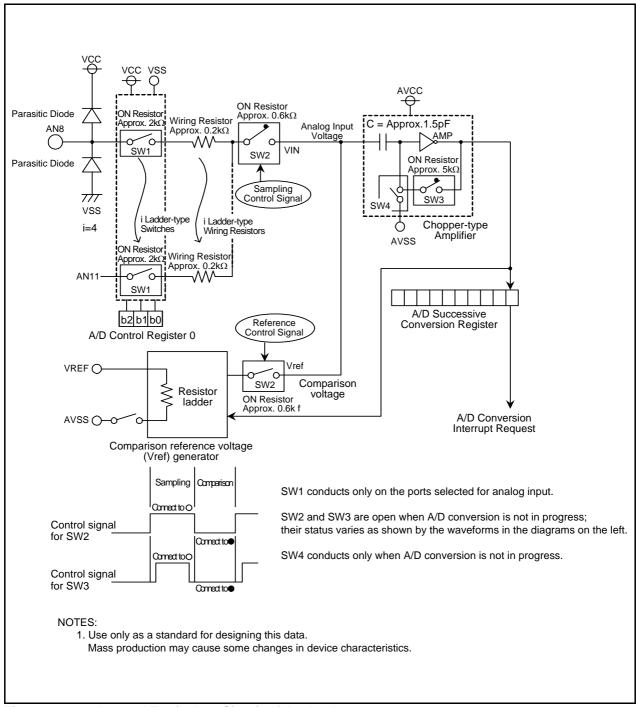

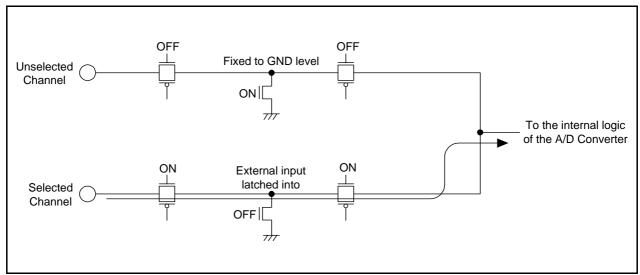

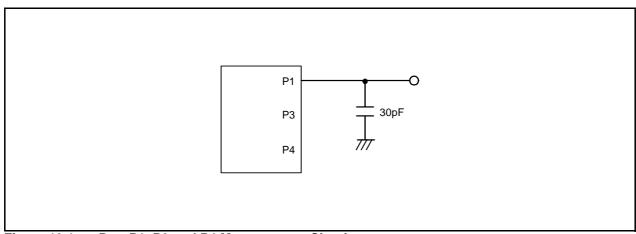

| 16  | 6.5  | Inte  | ernal Equivalent Circuit of Analog Input       | 177 |

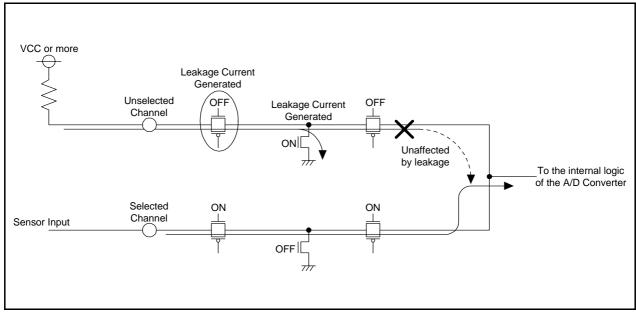

| 16  | 6.6  | Infl  | ow Current Bypass Circuit                      | 178 |

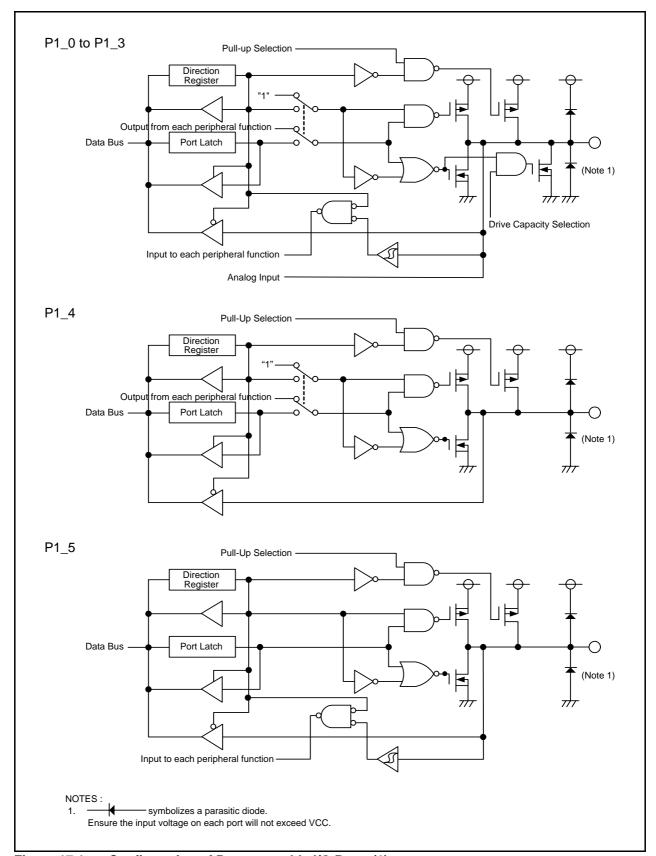

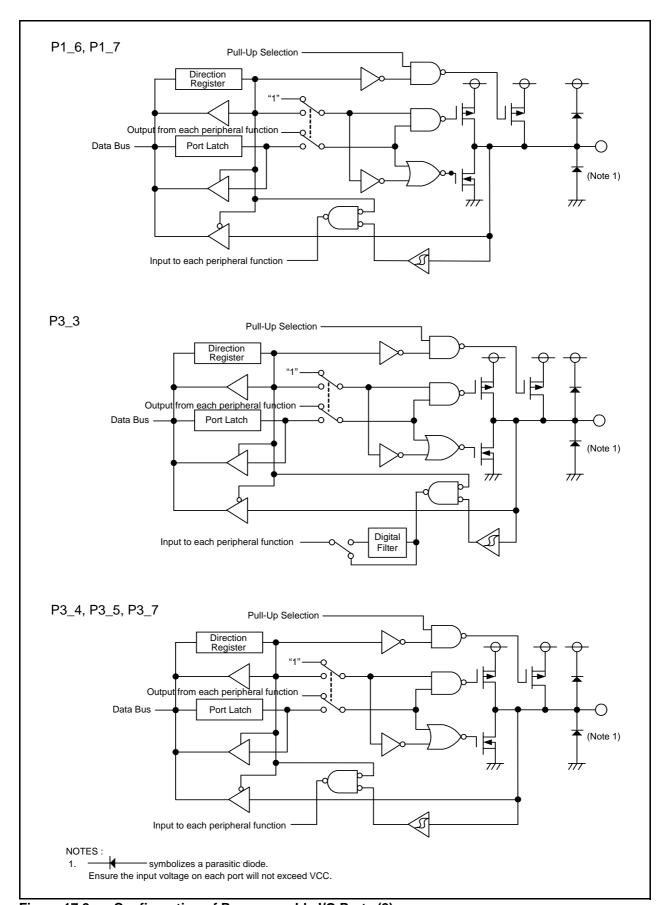

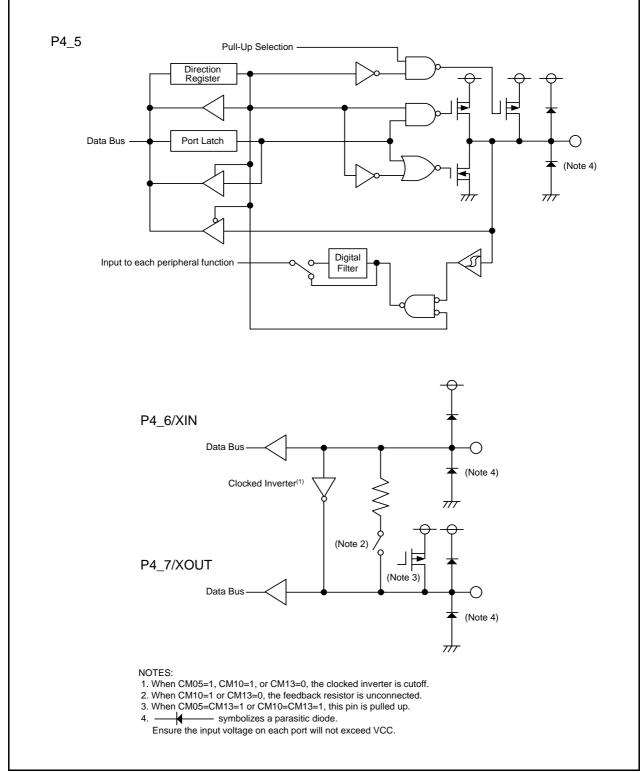

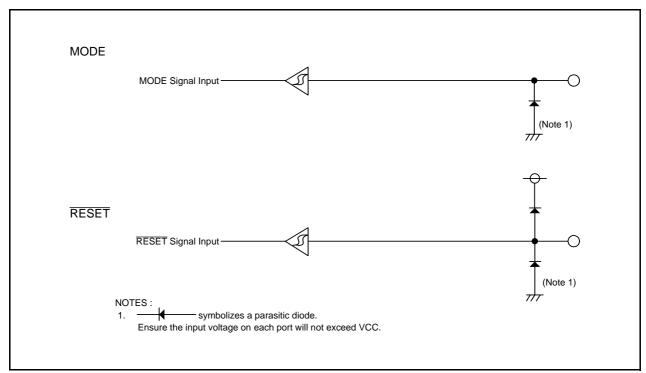

| 17. | Prog | grai  | mmable I/O Ports                               | 179 |

| 17  | 7.1  | Fui   | nctions of Programmable I/O Ports              | 179 |

| 17  | 7.2  | Eff   | ect on Peripheral Functions                    | 179 |

| 17  | 7.3  | Pin   | s Other than Programmable I/O Ports            | 179 |

| 17  | 7.4  | Po    | rt setting                                     | 186 |

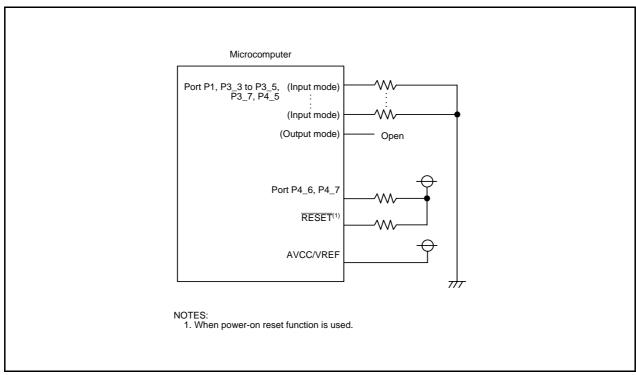

| 17  | 7.5  | Un    | assigned Pin Handling                          | 190 |

| 18. | Flas | sh N  | Memory Version                                 | 191 |

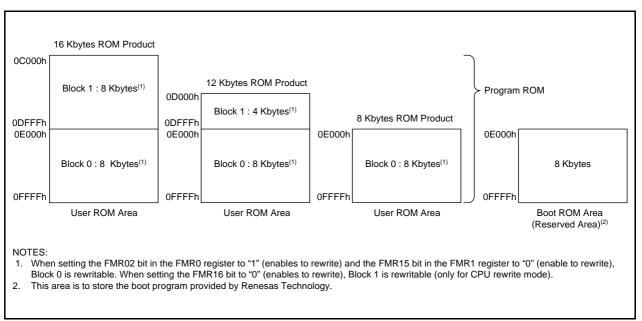

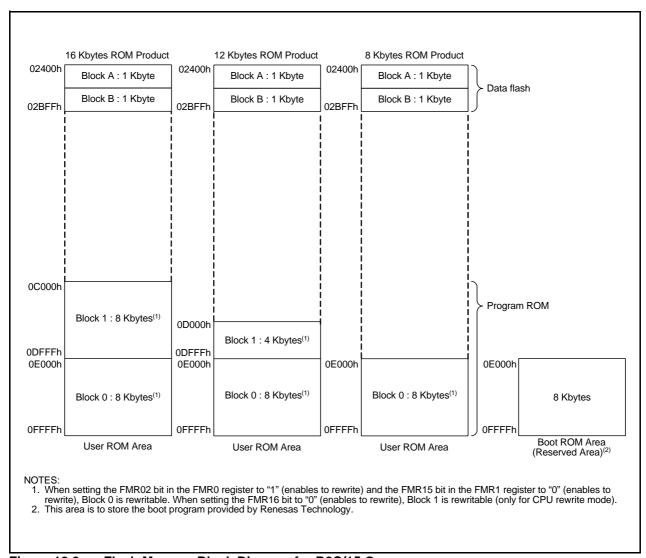

| 18  | 3.1  | Ov    | erview                                         | 191 |

| 18  | 3.2  | Ме    | mory Map                                       | 193 |

| 18  | 3.3  | Fui   | nctions To Prevent Flash Memory from Rewriting | 195 |

|     | 18.3 | 3.1   | ID Code Check Function                         | 195 |

|     | 18.3 | 3.2   | ROM Code Protect Function                      | 196 |

| 18  | 3.4  | СР    | U Rewrite Mode                                 | 197 |

|     | 18.4 | ŀ.1   | EW0 Mode                                       | 198 |

|     | 18.4 | .2    | EW1 Mode                                       | 198 |

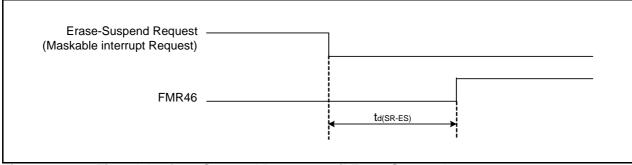

|     | 18.4 | 1.3   | Software Commands                              | 205 |

|     | 18.4 | 1.4   | Status Register                                | 209 |

|     | 18.4 | ł.5   | Full Status Check                              | 210 |

| 18  | 3.5  | Sta   | andard Serial I/O Mode                         | 212 |

|     | 18.5 | 5.1   | ID Code Check Function                         | 212 |

| 18  | 3.6  | Pa    | rallel I/O Mode                                | 216 |

|     | 18.6 | 5.1   | ROM Code Protect Function                      | 216 |

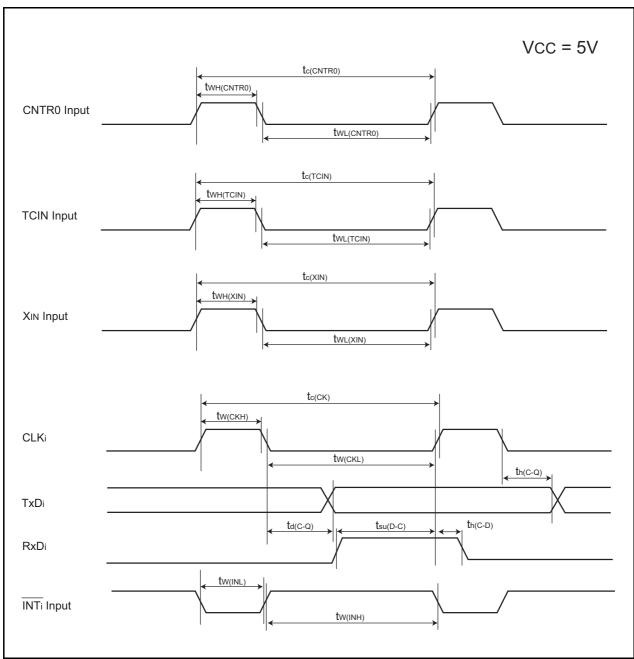

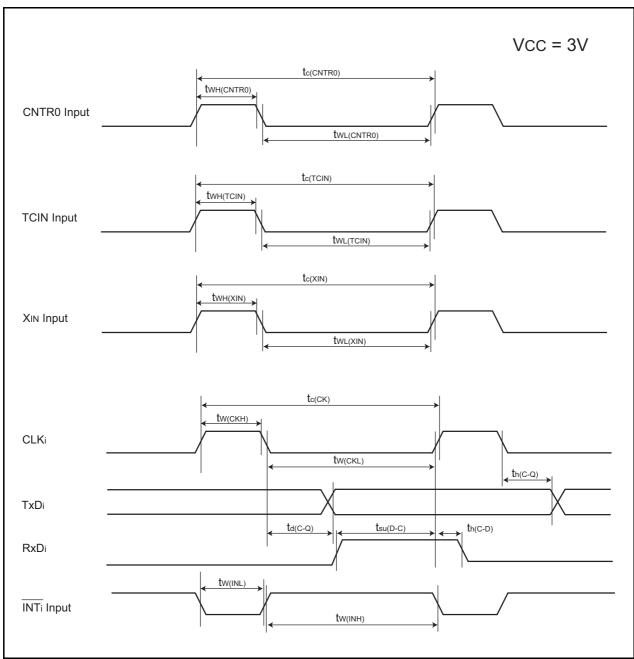

| 19. | Elec | ctric | cal Characteristics                            | 217 |

| 20. | Pre  | cau   | tions                                          | 235 |

| 20  | 0.1  | Sto   | pp Mode and Wait Mode                          | 235 |

|     | 20.1 | .1    | Stop Mode                                      | 235 |

|     | 20.1 | .2    | Wait Mode                                      | 235 |

| 20  | 0.2  | Inte  | errupts                                        | 236 |

| 20.2     | 2.1   | Reading Address 00000h                                                                               | 236      |

|----------|-------|------------------------------------------------------------------------------------------------------|----------|

| 20.2     | 2.2   | SP Setting                                                                                           | 236      |

| 20.2     | 2.3   | External Interrupt and Key Input Interrupt                                                           | 236      |

| 20.2     | 2.4   | Watchdog Timer Interrupt                                                                             | 236      |

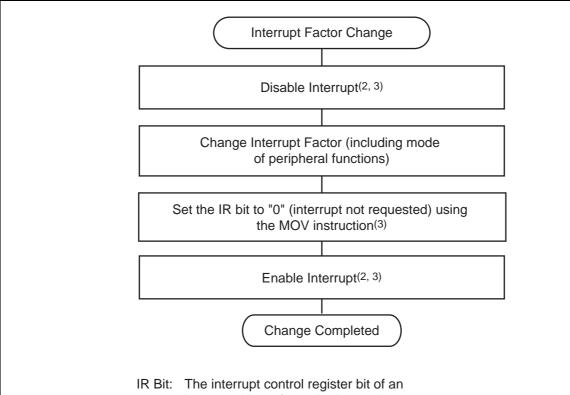

| 20.2     | 2.5   | Changing Interrupt Factor                                                                            | 237      |

| 20.2     | 2.6   | Changing Interrupt Control Register                                                                  | 238      |

| 20.3     | Clo   | ck Generation Circuit                                                                                | 239      |

| 20.3     | 3.1   | Oscillation Stop Detection Function                                                                  | 239      |

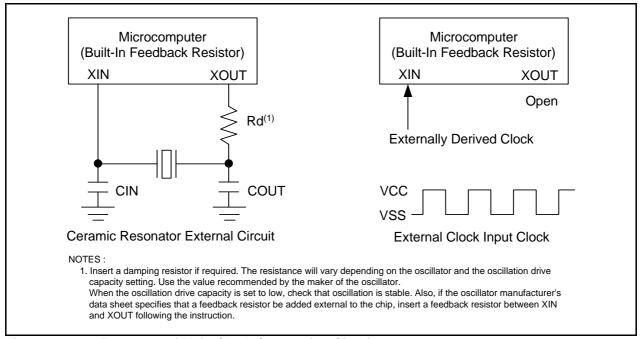

| 20.3     | 3.2   | Oscillation Circuit Constants                                                                        | 239      |

| 20.4     | Tim   | ners                                                                                                 | 240      |

| 20.4     | 4.1   | Timers X and Z                                                                                       | 240      |

| 20.4     | 4.2   | Timer X                                                                                              | 240      |

| 20.4     | 4.3   | Timer Z                                                                                              | 241      |

| 20.4     | 4.4   | Timer C                                                                                              | 241      |

| 20.5     | Ser   | ial Interface                                                                                        | 242      |

| 20.6     | Clo   | ck Synchronous Serial I/O (SSU) with Chip Select                                                     | 243      |

| 20.0     | 6.1   | Access Registers Associated with SSU                                                                 | 243      |

| 20.7     | A/D   | Converter                                                                                            | 244      |

| 20.8     | Flas  | sh Memory Version                                                                                    | 245      |

| 20.8     | 8.1   | CPU Rewrite Mode                                                                                     | 245      |

| 20.9     | Noi   | se                                                                                                   | 248      |

| 20.9     | 9.1   | Insert a bypass capacitor between VCC and VSS pins as the countermeasures against noise and latch-up | 248      |

| 20.9     | 9.2   | Countermeasures against Noise Error of Port Control Registers                                        | 248      |

| 21. Pre  | caut  | tion for On-chip Debugger                                                                            | 249      |

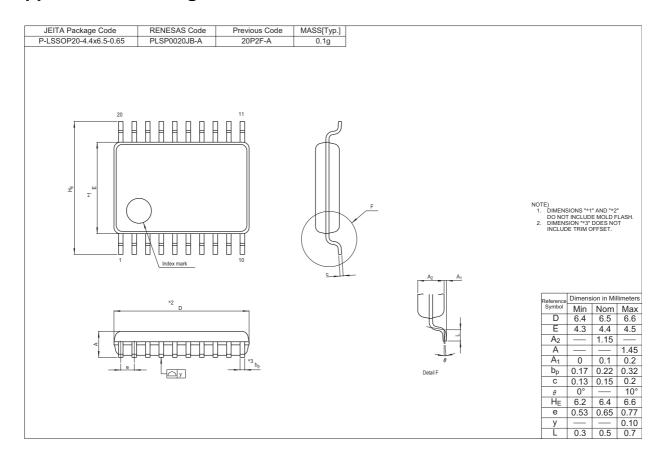

| Append   | ix 1. | Package Dimensions                                                                                   | 250      |

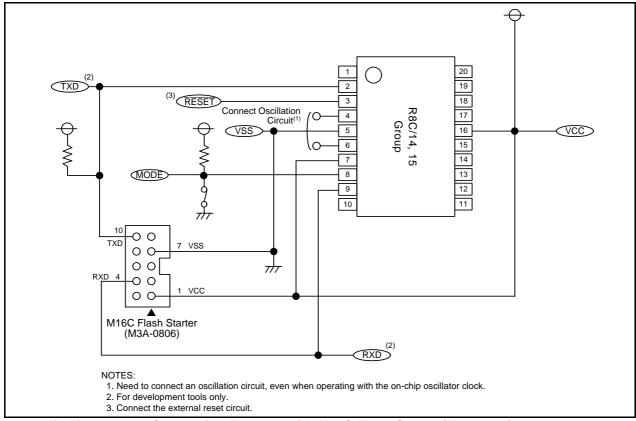

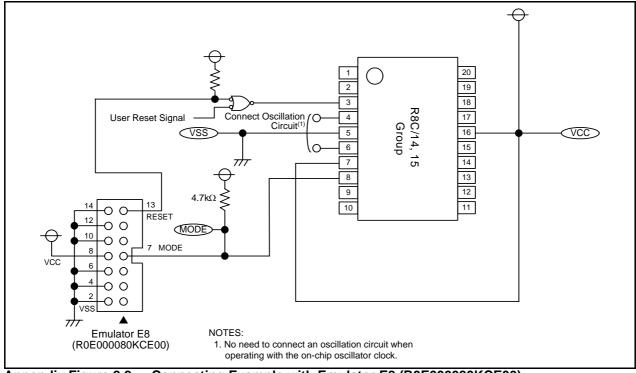

| Append   | ix 2. | Connecting Example between Serial Writer and On-Chip Debugging Emulator                              | p<br>251 |

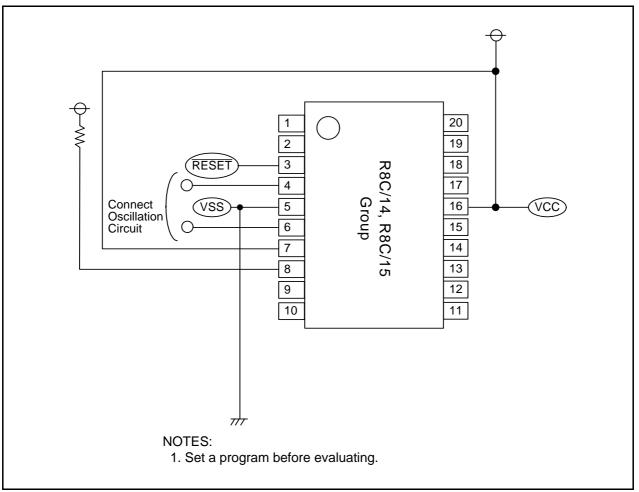

| Append   | ix 3. | Example of Oscillation Evaluation Circuit                                                            | 252      |

| Register | r Ind | ex                                                                                                   | 253      |

# **SFR Page Reference**

|                                                                                                                                              | Register                                                                 | Symbol       | Page     |

|----------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|--------------|----------|

| 0000h                                                                                                                                        |                                                                          |              |          |

| 0001h                                                                                                                                        |                                                                          |              |          |

| 0002h                                                                                                                                        |                                                                          |              |          |

| 0003h                                                                                                                                        |                                                                          |              |          |

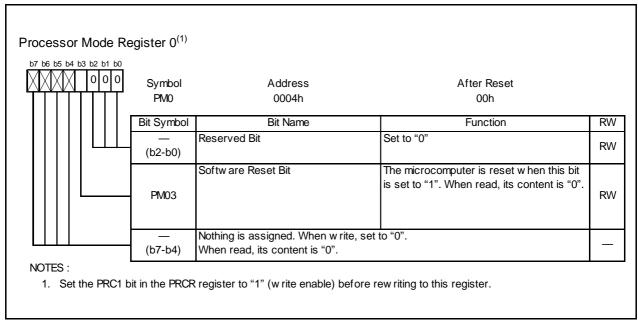

| 0004h                                                                                                                                        | Processor Mode Register 0                                                | PM0          | 35       |

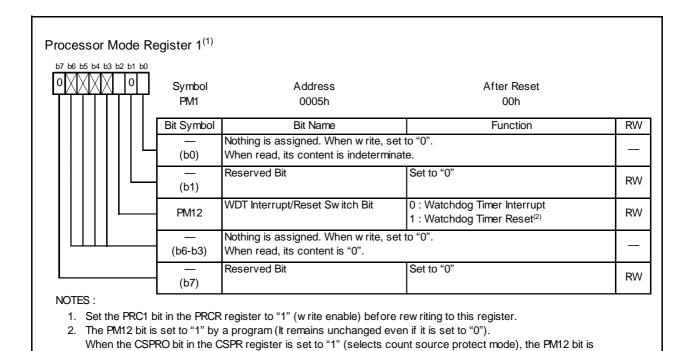

| 0005h                                                                                                                                        | Processor Mode Register 1                                                | PM1          | 36       |

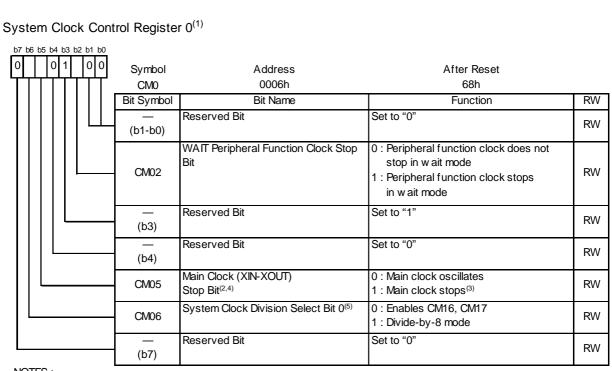

| 0006h                                                                                                                                        | System Clock Control Register 0                                          | CM0          | 40       |

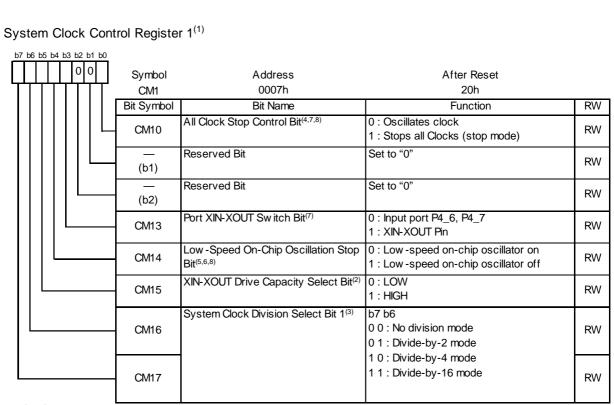

| 0007h                                                                                                                                        | System Clock Control Register 1                                          | CM1          | 41       |

| 0008h                                                                                                                                        |                                                                          | <b>-</b>     |          |

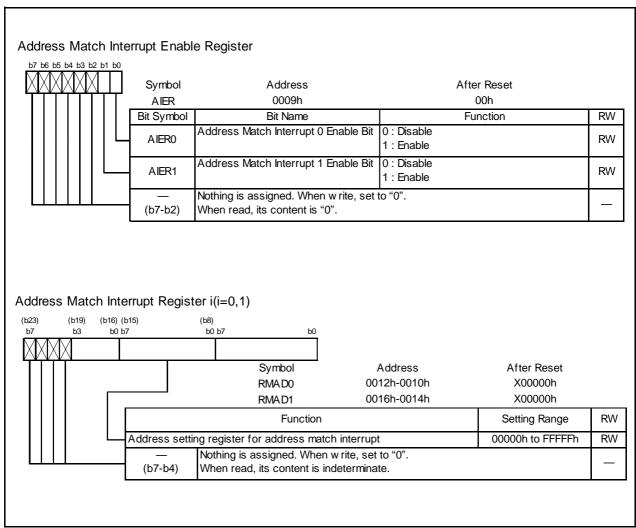

| 0009h                                                                                                                                        | Address Match Interrupt Enable Register                                  | AIER         | 77       |

| 000Ah                                                                                                                                        | Protect Register                                                         | PRCR         | 55       |

| 000Bh                                                                                                                                        |                                                                          |              |          |

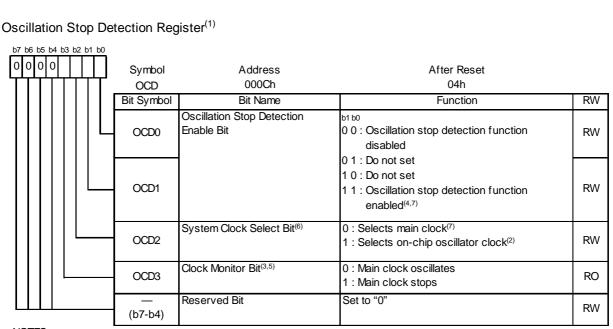

| 000Ch                                                                                                                                        | Oscillation Stop Detection Register                                      | OCD          | 42       |

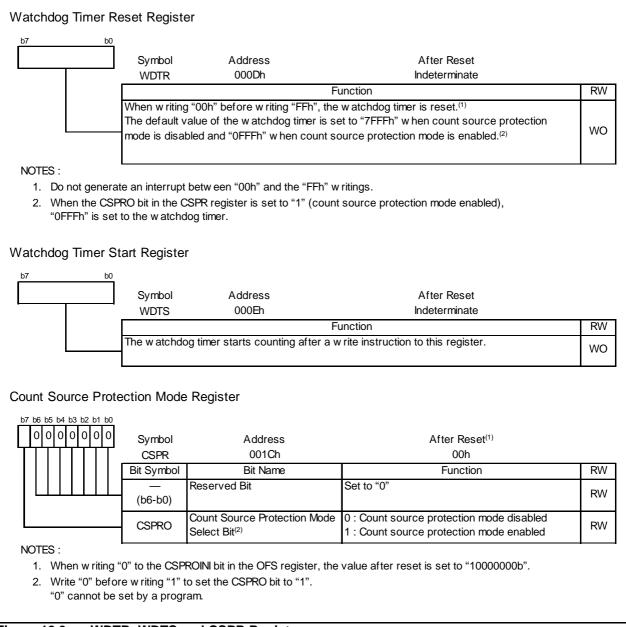

| 000Dh                                                                                                                                        | Watchdog Timer Reset Register                                            | WDTR         | 80       |

| 000Eh                                                                                                                                        | Watchdog Timer Start Register                                            | WDTS         | 80       |

| 000Fh                                                                                                                                        | Watchdog Timer Control Register                                          | WDC          | 79       |

| 0010h                                                                                                                                        | Address Match Interrupt Register 0                                       | RMAD0        | 77       |

| 0011h                                                                                                                                        |                                                                          |              |          |

| 0012h                                                                                                                                        |                                                                          |              |          |

| 0013h                                                                                                                                        |                                                                          | 51415        |          |

| 0014h                                                                                                                                        | Address Match Interrupt Register 1                                       | RMAD1        | 77       |

| 0015h                                                                                                                                        |                                                                          |              |          |

| 0016h                                                                                                                                        |                                                                          |              |          |

| 0017h                                                                                                                                        |                                                                          |              |          |

| 0018h                                                                                                                                        |                                                                          |              |          |

| 0019h                                                                                                                                        |                                                                          |              |          |

| 001Ah                                                                                                                                        |                                                                          |              |          |

| 001Bh                                                                                                                                        |                                                                          |              |          |

| 001Ch                                                                                                                                        | Count Source Protection Mode Register                                    | CSPR         | 80       |

| 001Dh                                                                                                                                        |                                                                          |              |          |

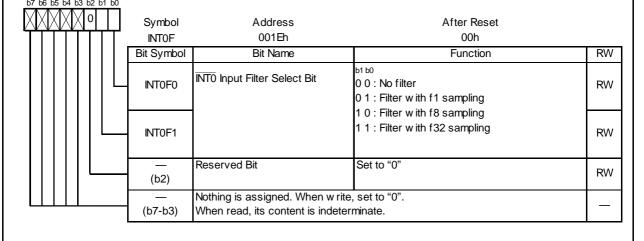

| 001Eh                                                                                                                                        | INT0 Input Filter Select Register                                        | INT0F        | 69       |

| 001Fh                                                                                                                                        |                                                                          |              |          |

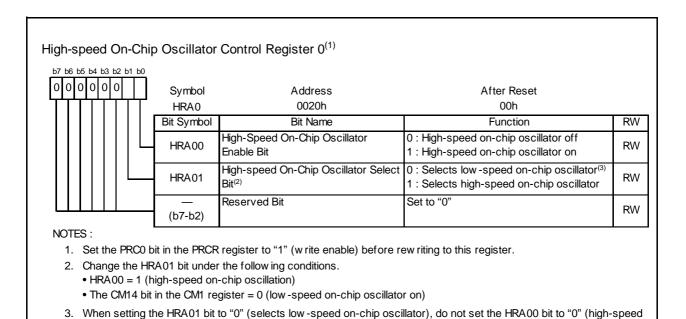

| 0020h                                                                                                                                        | High-Speed On-Chip Oscillator Control                                    | HRA0         | 43       |

|                                                                                                                                              | Register 0                                                               |              |          |

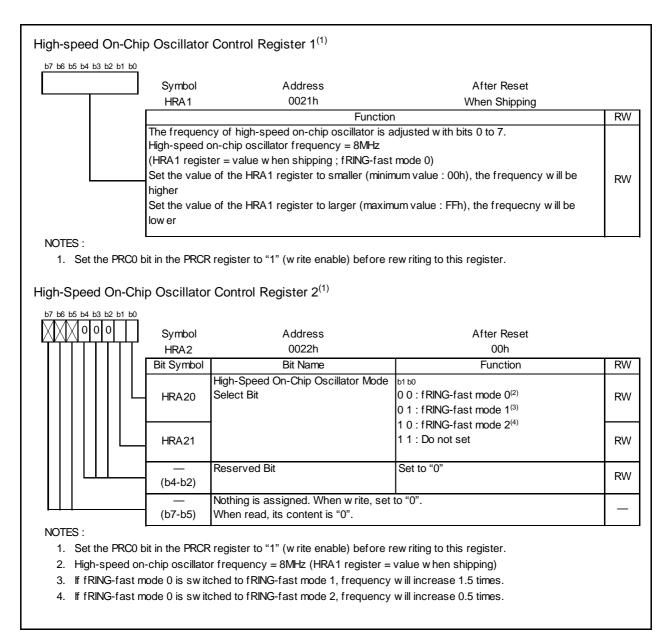

| 0021h                                                                                                                                        | High-Speed On-Chip Oscillator Control Register 1                         | HRA1         | 44       |

| 0022h                                                                                                                                        | High-Speed On-Chip Oscillator Control<br>Register 2                      | HRA2         | 44       |

| 0023h                                                                                                                                        | ,                                                                        |              |          |

| 0024h                                                                                                                                        |                                                                          |              |          |

| 0025h                                                                                                                                        |                                                                          |              |          |

| 0026h                                                                                                                                        |                                                                          |              |          |

| 0027h                                                                                                                                        |                                                                          |              |          |

| 0028h                                                                                                                                        |                                                                          |              |          |

|                                                                                                                                              |                                                                          |              |          |

| 0029h                                                                                                                                        |                                                                          | 1            |          |

|                                                                                                                                              |                                                                          |              |          |

| 002Ah                                                                                                                                        |                                                                          |              |          |

| 002Ah<br>002Bh                                                                                                                               |                                                                          |              |          |

| 002Ah<br>002Bh<br>002Ch                                                                                                                      |                                                                          |              |          |

| 002Ah<br>002Bh<br>002Ch<br>002Dh                                                                                                             |                                                                          |              |          |

| 002Ah<br>002Bh<br>002Ch<br>002Dh<br>002Eh                                                                                                    |                                                                          |              |          |

| 0029h<br>002Ah<br>002Bh<br>002Ch<br>002Dh<br>002Eh<br>002Fh                                                                                  |                                                                          |              |          |

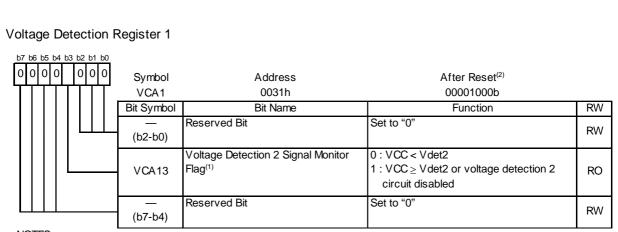

| 002Ah<br>002Bh<br>002Ch<br>002Dh<br>002Eh<br>002Fh<br>0030h                                                                                  | Voltage Detection Register 1                                             | VCA1         | 28       |

| 002Ah<br>002Bh<br>002Ch<br>002Dh<br>002Eh<br>002Fh<br>0030h                                                                                  | Voltage Detection Register 1 Voltage Detection Register 2                |              |          |

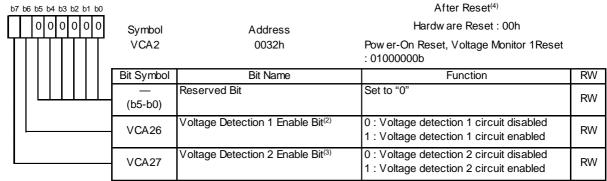

| 002Ah<br>002Bh<br>002Ch<br>002Dh<br>002Eh<br>002Fh<br>0030h<br>0031h                                                                         | Voltage Detection Register 1 Voltage Detection Register 2                | VCA1<br>VCA2 | 28<br>28 |

| 002Ah<br>002Bh<br>002Ch<br>002Dh<br>002Eh<br>002Fh<br>0030h<br>0031h<br>0032h                                                                |                                                                          |              |          |

| 002Ah<br>002Bh<br>002Ch<br>002Ch<br>002Eh<br>002Fh<br>0030h<br>0031h<br>0032h<br>0033h                                                       |                                                                          |              |          |

| 002Ah<br>002Bh<br>002Ch<br>002Dh<br>002Eh<br>002Fh<br>0030h<br>0031h<br>0032h<br>0033h<br>0034h                                              | Voltage Detection Register 2                                             | VCA2         | 28       |

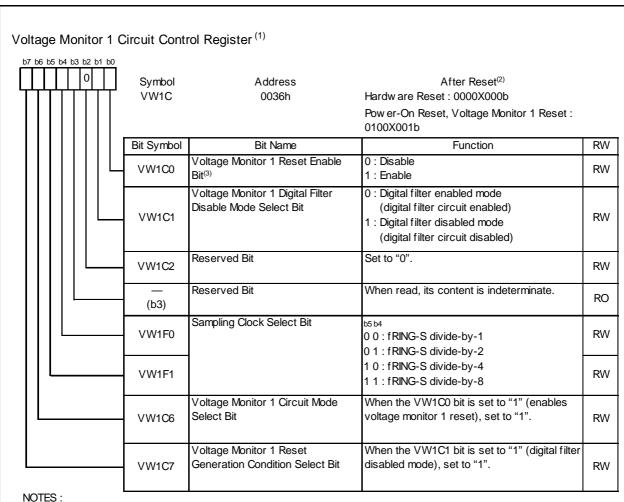

| 002Ah<br>002Bh<br>002Ch<br>002Dh<br>002Eh<br>002Fh<br>0030h<br>0031h<br>0032h<br>0033h<br>0034h<br>0035h                                     | Voltage Detection Register 2  Voltage Monitor 1 Circuit Control Register | VCA2         | 28       |

| 002Ah<br>002Bh<br>002Ch<br>002Dh<br>002Eh<br>002Fh<br>0030h<br>0031h<br>0032h<br>0033h<br>0034h<br>0035h<br>0036h                            | Voltage Detection Register 2                                             | VCA2         | 28       |

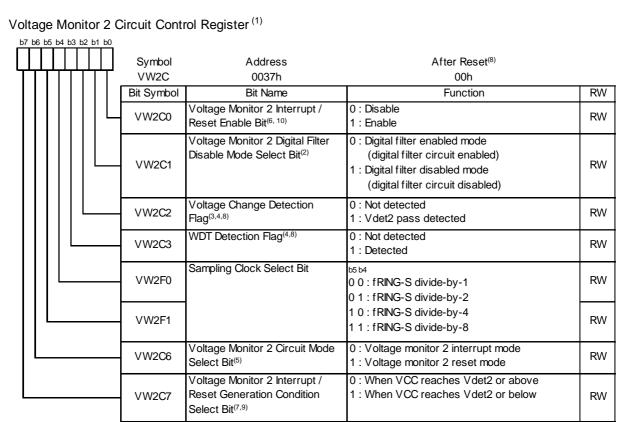

| 002Ah<br>002Bh<br>002Ch<br>002Dh<br>002Eh<br>002Fh<br>0031h<br>0032h<br>0033h<br>0034h<br>0035h<br>0036h                                     | Voltage Detection Register 2  Voltage Monitor 1 Circuit Control Register | VCA2         | 28       |

| 002Ah<br>002Bh<br>002Ch<br>002Dh<br>002Eh<br>002Eh<br>0030h<br>0031h<br>0032h<br>0033h<br>0034h<br>0035h<br>0036h<br>0037h                   | Voltage Detection Register 2  Voltage Monitor 1 Circuit Control Register | VCA2         | 28       |

| 002Ah<br>002Bh<br>002Ch<br>002Ch<br>002Dh<br>002Fh<br>0030h<br>0031h<br>0032h<br>0033h<br>0034h<br>0035h<br>0036h<br>0037h<br>0038h          | Voltage Detection Register 2  Voltage Monitor 1 Circuit Control Register | VCA2         | 28       |

| 002Ah 002Bh 002Ch 002Ch 002Ph 002Fh 0030h 0031h 0032h 0033h 0034h 0035h 0036h 0037h 0038h 0038h 0038h 0038h                                  | Voltage Detection Register 2  Voltage Monitor 1 Circuit Control Register | VCA2         | 28       |

| 002Ah<br>002Bh<br>002Ch<br>002Ch<br>002Ch<br>002Fh<br>0031h<br>0031h<br>0033h<br>0034h<br>0035h<br>0036h<br>0036h<br>0036h<br>0036h<br>0036h | Voltage Detection Register 2  Voltage Monitor 1 Circuit Control Register | VCA2         | 28       |

| 002Ah<br>002Bh<br>002Ch<br>002Ch<br>002Dh<br>002Fh<br>0030h<br>0031h<br>0032h<br>0033h<br>0034h<br>0035h<br>0036h<br>0037h<br>0038h          | Voltage Detection Register 2  Voltage Monitor 1 Circuit Control Register | VCA2         | 28       |

| Address        | Register                                  | Symbol | Page                                             |

|----------------|-------------------------------------------|--------|--------------------------------------------------|

| 0040h          | register                                  | Cymbol | , age                                            |

| 0041h          |                                           |        | -                                                |

| 0042h          |                                           |        | +                                                |

| 0043h          |                                           |        |                                                  |

| 0044h          |                                           |        | +                                                |

| 0045h          |                                           |        |                                                  |

| 0046h          |                                           |        |                                                  |

| 0047h          |                                           |        | 1                                                |

| 0048h          |                                           |        |                                                  |

| 0049h          |                                           |        |                                                  |

| 004Ah          |                                           |        |                                                  |

| 004Bh          |                                           |        |                                                  |

| 004Ch          |                                           |        |                                                  |

| 004Dh          | Key Input Interrupt Control Register      | KUPIC  | 61                                               |

| 004Eh          | A/D Conversion Interrupt Control Register | ADIC   | 61                                               |

| 004Fh          | SSU Interrupt Control Register            | SSUAIC | 61                                               |

| 0050h          | Compare 1 Interrupt Control Register      | CMP1IC | 61                                               |

| 0051h          | UART0 Transmit Interrupt Control Register | S0TIC  | 61                                               |

| 0052h          | UARTO Receive Interrupt Control Register  | S0RIC  | 61                                               |

| 0053h          | ·                                         |        |                                                  |

| 0054h          |                                           |        |                                                  |

| 0055h          |                                           |        |                                                  |

| 0056h          | Timer X Interrupt Control Register        | TXIC   | 61                                               |

| 0057h          |                                           |        |                                                  |

| 0058h          | Timer Z Interrupt Control Register        | TZIC   | 61                                               |

| 0059h          | INT1 Interrupt Control Register           | INT1IC | 61                                               |

| 005Ah          | INT3 Interrupt Control Register           | INT3IC | 61                                               |

| 005Bh          | ı                                         | TCIC   | 61                                               |

| 005Ch          | Timer C Interrupt Control Register        | CMP0IC | 61                                               |

|                | Compare 0 Interrupt Control Register      | INTOIC | 62                                               |

| 005Dh          | INTO Interrupt Control Register           | INTOIC | 62                                               |

| 005Eh          |                                           |        |                                                  |

| 005Fh          |                                           |        |                                                  |

| 0060h          |                                           |        |                                                  |

| 0061h          |                                           |        |                                                  |

| 0062h          |                                           |        |                                                  |

| 0063h          |                                           |        |                                                  |

| 0064h          |                                           |        |                                                  |

| 0065h          |                                           |        |                                                  |

| 0066h          |                                           |        |                                                  |

| 0067h          |                                           |        |                                                  |

| 0068h          |                                           |        |                                                  |

| 0069h          |                                           |        |                                                  |

| 006Ah          |                                           |        |                                                  |

| 006Bh<br>006Ch |                                           |        |                                                  |

| 006Ch          |                                           | +      | 1                                                |

| 006Eh          |                                           | +      | 1                                                |

| 006Eh          |                                           | +      | 1                                                |

| 0070h          |                                           | +      |                                                  |

| 0070h          |                                           | +      | <del>                                     </del> |

| 0071h          |                                           | +      | <del> </del>                                     |

| 0072H          |                                           |        |                                                  |

| 0073H          |                                           | +      | <del> </del>                                     |

| 0074H          |                                           | +      | +                                                |

| 0075h          |                                           |        | +                                                |

| 0070H          |                                           | +      | +                                                |

| 0077H          |                                           |        | +                                                |

| 0079h          |                                           |        |                                                  |

| 0073h          |                                           |        | +                                                |

| 007An          |                                           | +      | †                                                |

| 007Ch          |                                           |        | +                                                |

| 007Dh          |                                           | +      | †                                                |

| 007Eh          |                                           | +      | †                                                |

| 007En          |                                           |        | +                                                |

| 33.111         |                                           | I      | <u> </u>                                         |

## NOTES:

Blank columns are all reserved space. No access is allowed.

| Address |                                           |       | Page   |

|---------|-------------------------------------------|-------|--------|

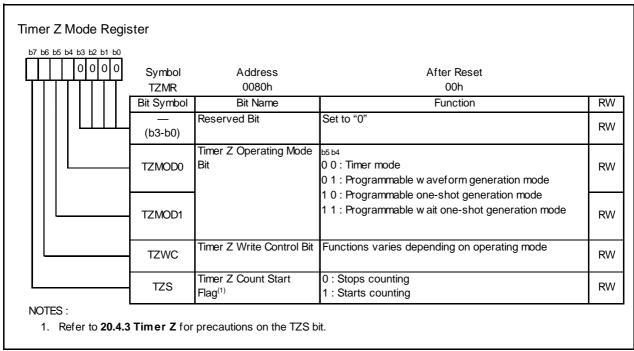

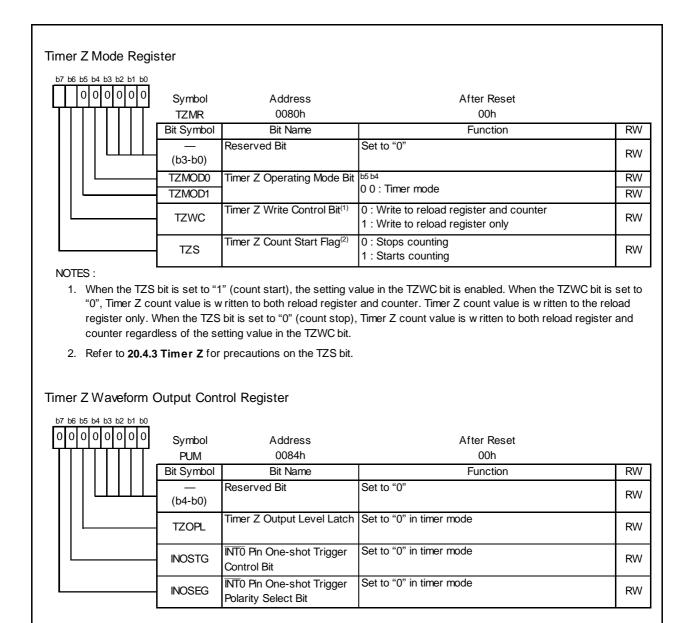

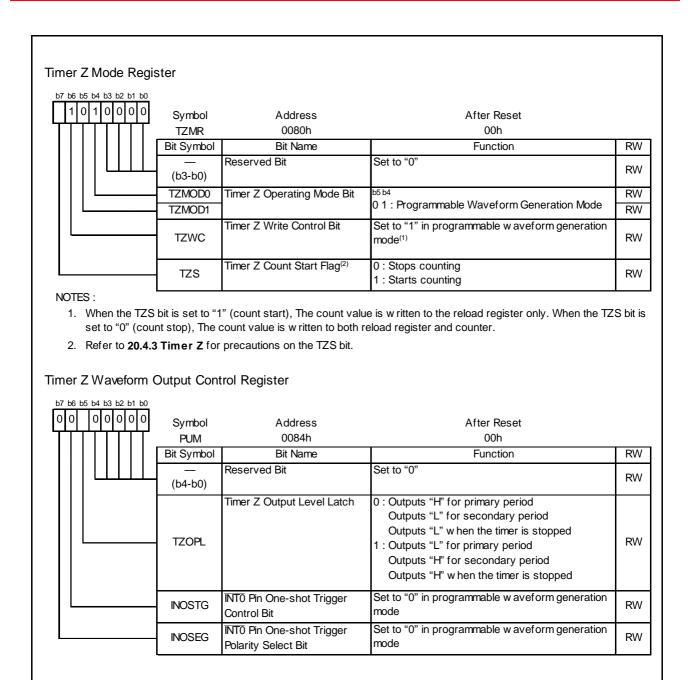

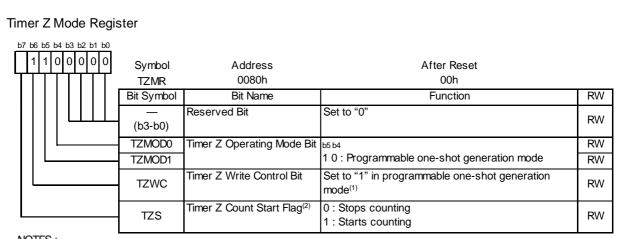

| 0080h   | Timer Z Mode Register                     | TZMR  | 99     |

| 0081h   |                                           |       |        |

| 0082h   |                                           |       |        |

| 0083h   |                                           |       |        |

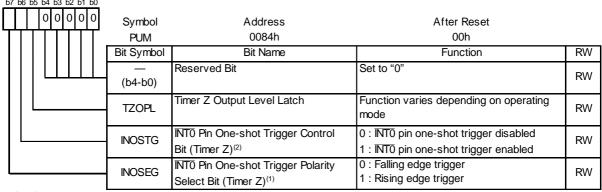

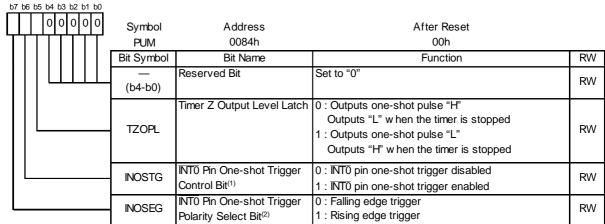

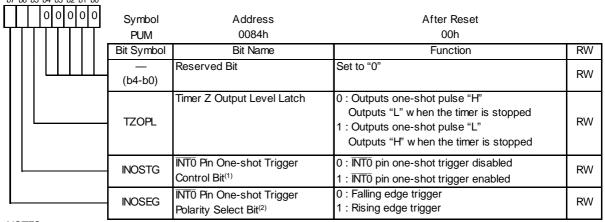

| 0084h   | Timer Z Waveform Output Control Register  | PUM   | 101    |

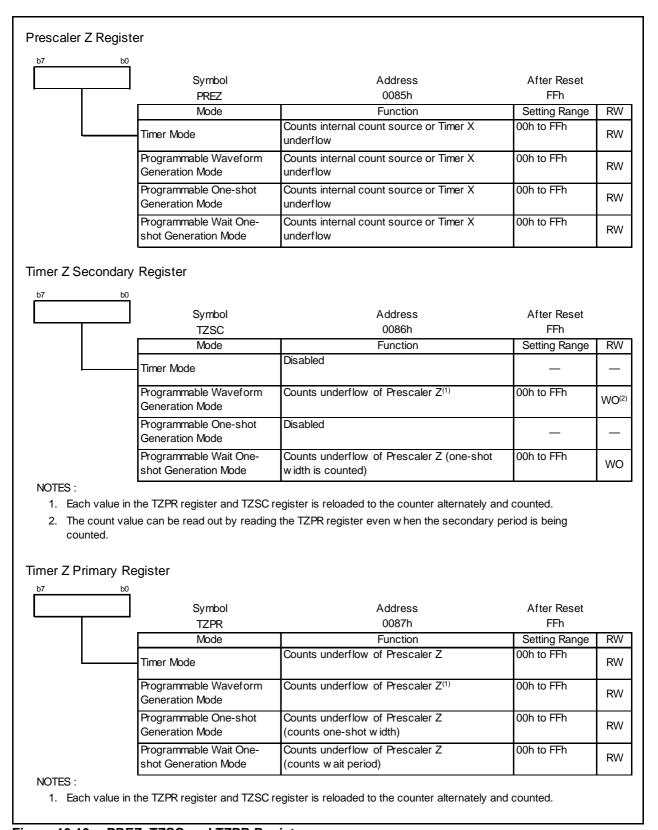

| 0085h   | Prescaler Z                               | PREZ  | 100    |

| 0086h   | Timer Z Secondary                         | TZSC  | 100    |

| 0087h   | Timer Z Primary                           | TZPR  | 100    |

| 0088h   |                                           |       |        |

| 0089h   |                                           |       |        |

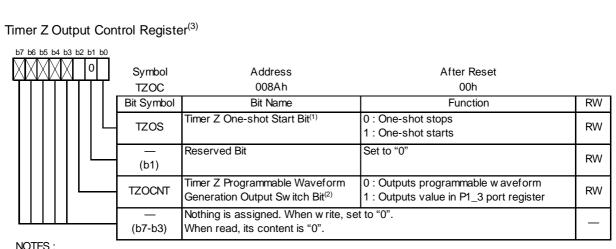

| 008Ah   | Timer Z Output Control Register           | TZOC  | 101    |

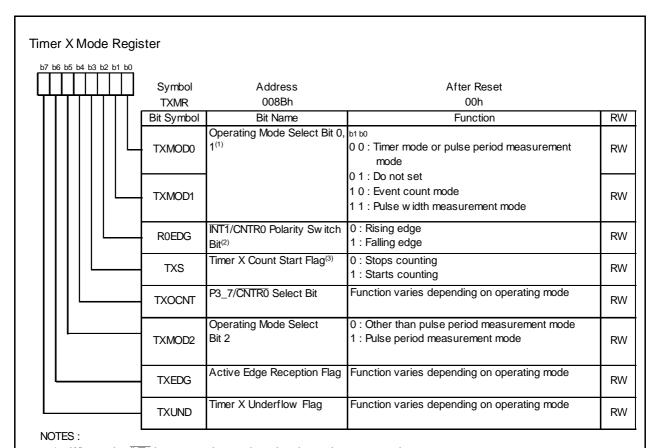

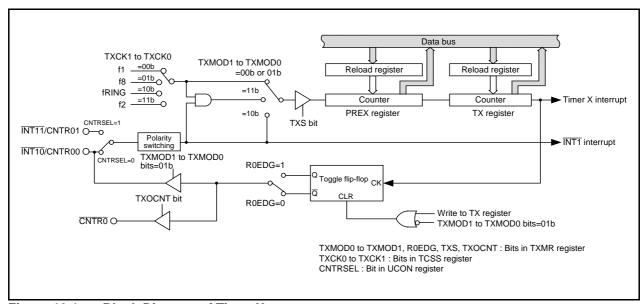

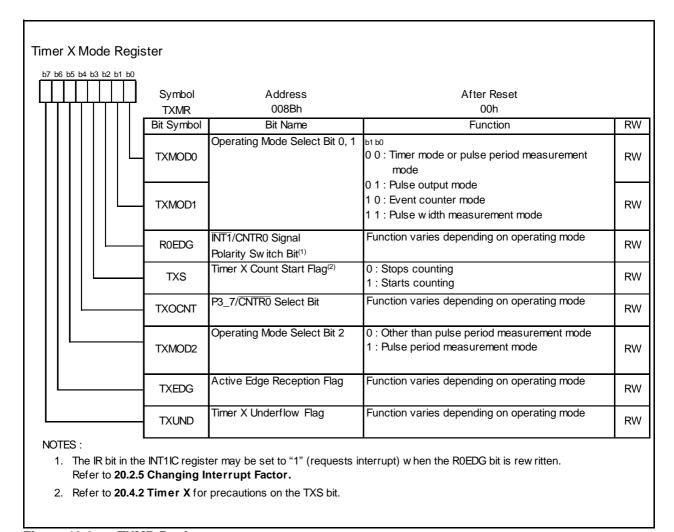

| 008Bh   | Timer X Mode Register                     | TXMR  | 85     |

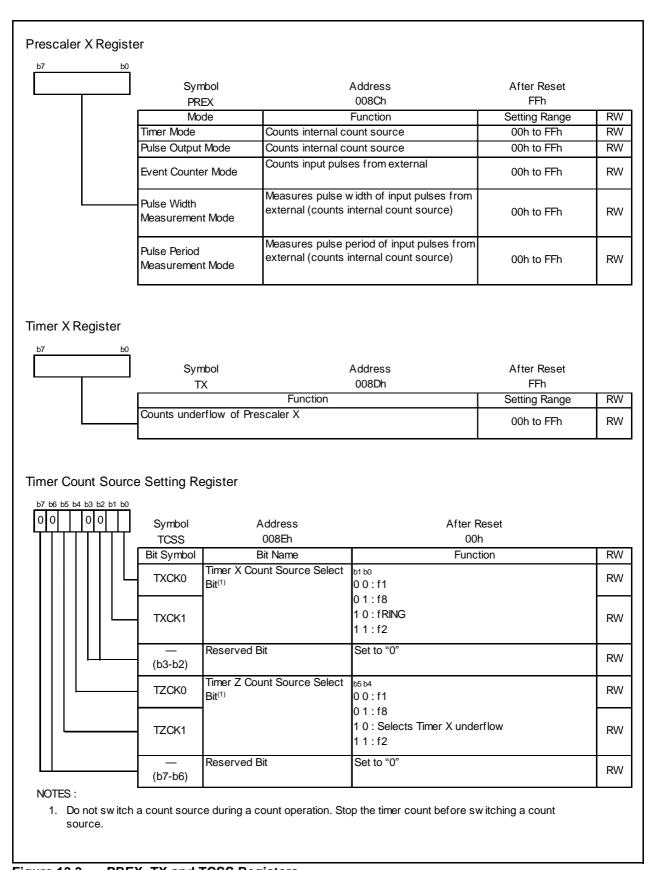

| 008Ch   | Prescaler X                               | PREX  | 86     |

| 008Dh   | Timer X                                   | TX    | 86     |

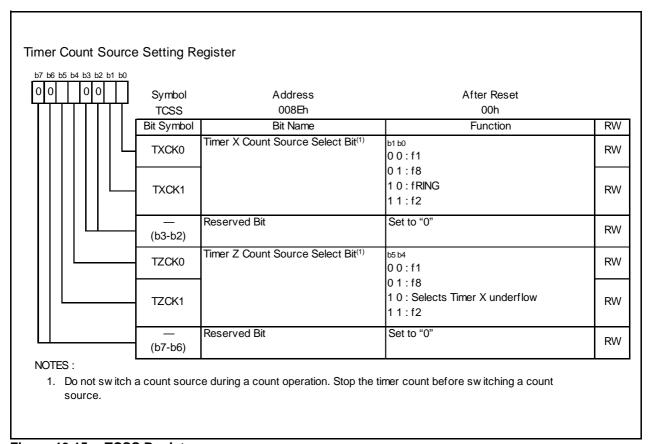

| 008Eh   | Timer Count Source Set Register           | TCSS  | 86,102 |

| 008Fh   |                                           |       |        |

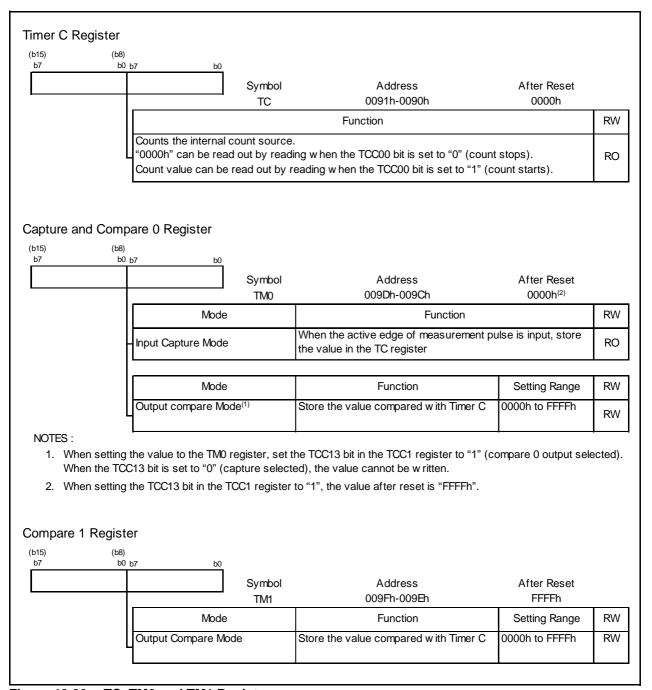

| 0090h   | Timer C                                   | TC    | 117    |

| 0091h   |                                           |       |        |

| 0092h   |                                           |       |        |

| 0093h   |                                           |       |        |

| 0094h   |                                           |       |        |

| 0095h   |                                           |       |        |

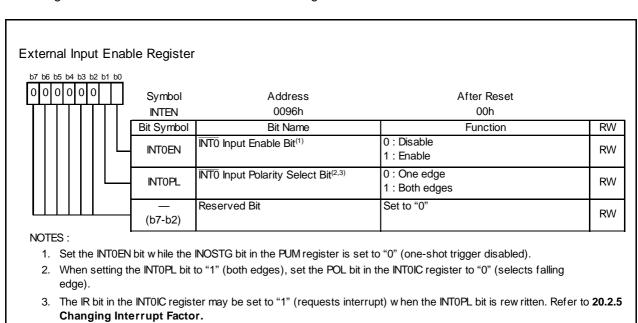

| 0096h   | External Input Enable Register            | INTEN | 69     |

| 0097h   |                                           |       |        |

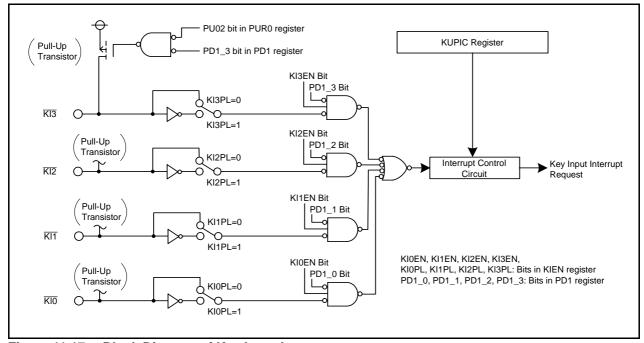

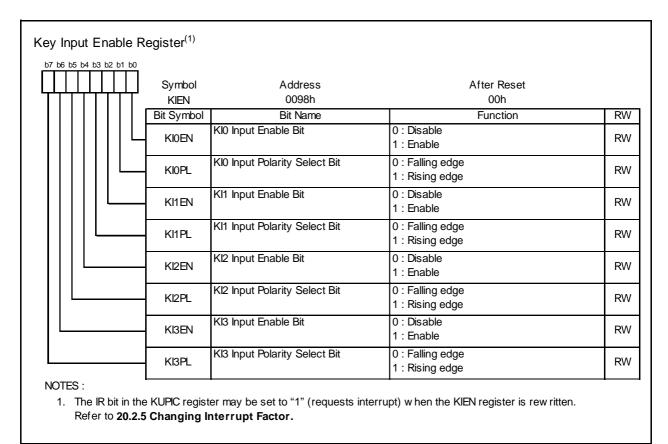

| 0098h   | Key Input Enable Register                 | KIEN  | 75     |

| 0099h   |                                           |       |        |

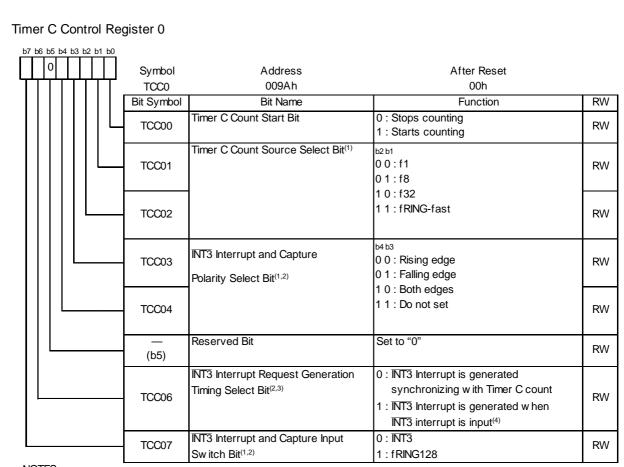

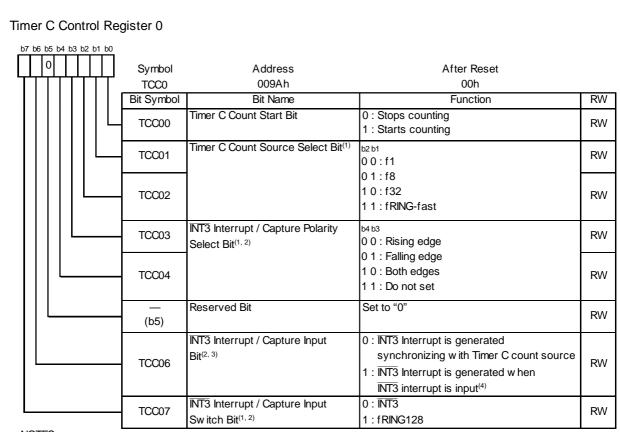

| 009Ah   | Timer C Control Register 0                | TCC0  | 118    |

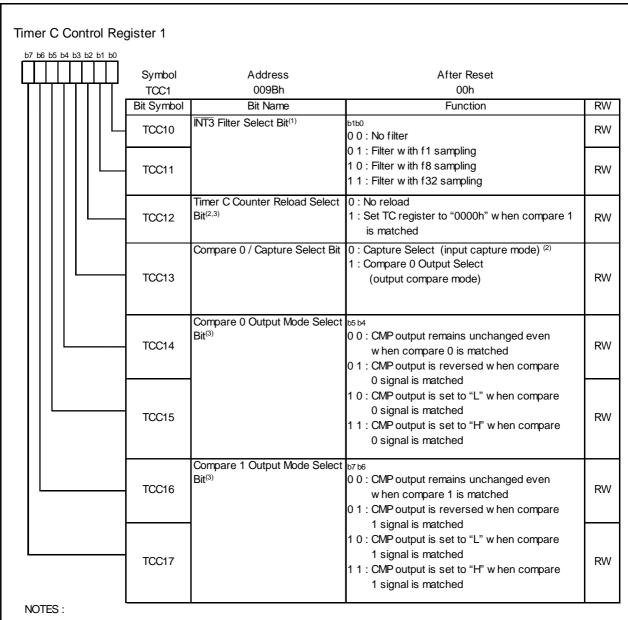

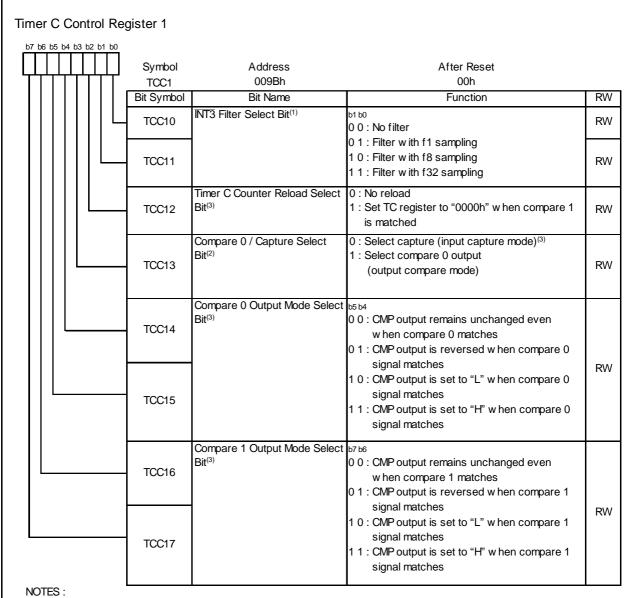

| 009Bh   | Timer C Control Register 1                | TCC1  | 119    |

| 009Ch   | Capture, Compare 0 Register               | TM0   | 117    |

| 009Dh   |                                           |       |        |

| 009Eh   | Compare 1 Register                        | TM1   | 117    |

| 009Fh   |                                           |       |        |

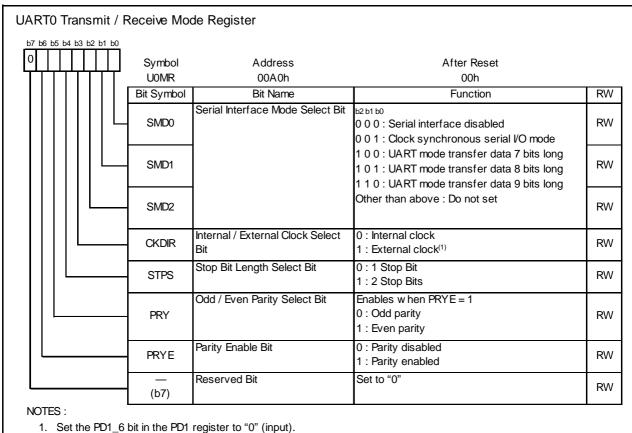

| 00A0h   | UART0 Transmit/Receive Mode Register      | U0MR  | 128    |

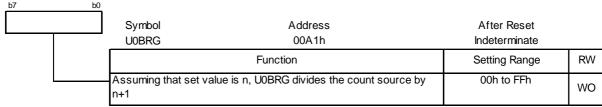

| 00A1h   | UART0 Bit Rate Register                   | U0BRG | 127    |

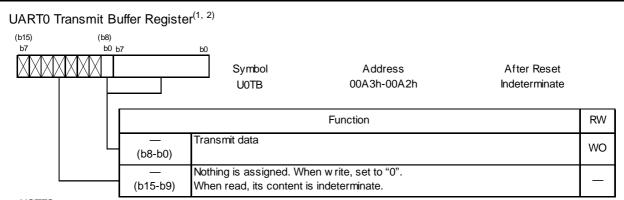

| 00A2h   | UART0 Transmit Buffer Register            | U0TB  | 127    |

| 00A3h   |                                           |       |        |

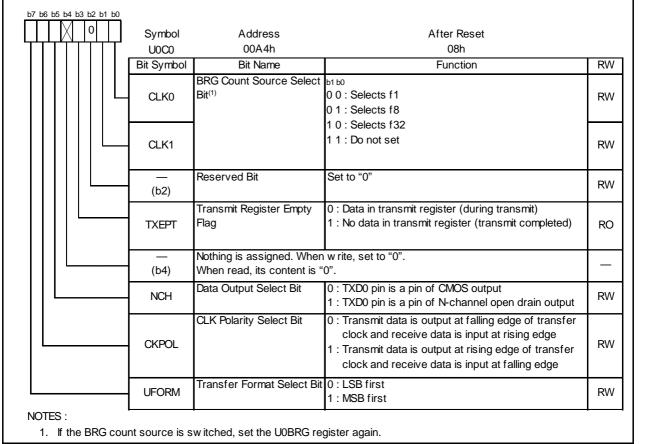

| 00A4h   | UART0 Transmit/Receive Control Register 0 | U0C0  | 128    |

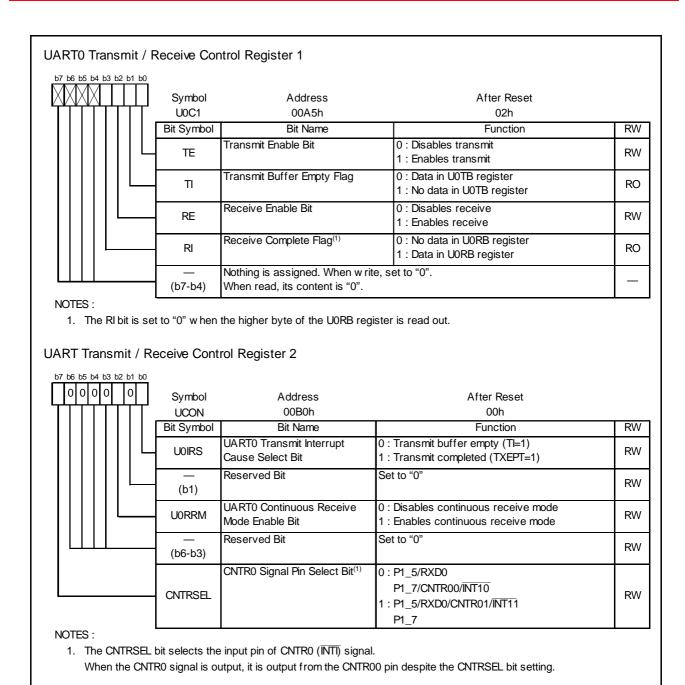

| 00A5h   | UART0 Transmit/Receive Control Register 1 | U0C1  | 129    |

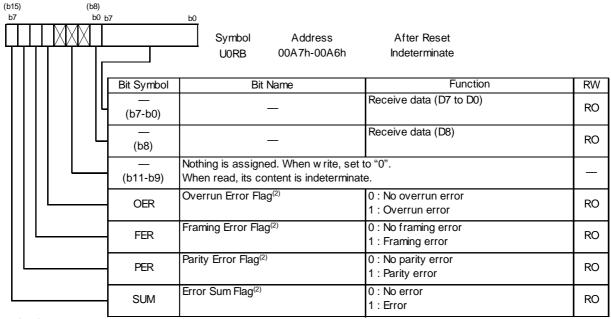

| 00A6h   | UART0 Receive Buffer Register             | U0RB  | 127    |

| 00A7h   | 1                                         |       |        |

| 00A8h   |                                           |       |        |

| 00A9h   |                                           |       |        |

| 00AAh   |                                           |       |        |

| 00ABh   |                                           |       |        |

| 00ACh   |                                           |       |        |

| 00ADh   |                                           |       |        |

| 00AEh   |                                           |       |        |

| 00AFh   |                                           |       |        |

| 00B0h   | UART Transmit/Receive Control Register 2  | UCON  | 129    |

| 00B1h   | <u> </u>                                  |       | 1      |

| 00B2h   |                                           |       | 1      |

| 00B3h   |                                           |       |        |

| 00B4h   |                                           |       |        |

| 00B5h   |                                           |       | 1      |

| 00B6h   |                                           | 1     |        |

| 00B7h   |                                           | 1     |        |

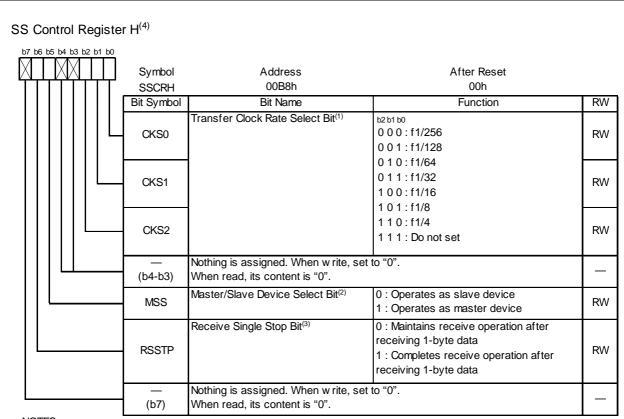

| 00B8h   | SS Control Register H                     | SSCRH | 142    |

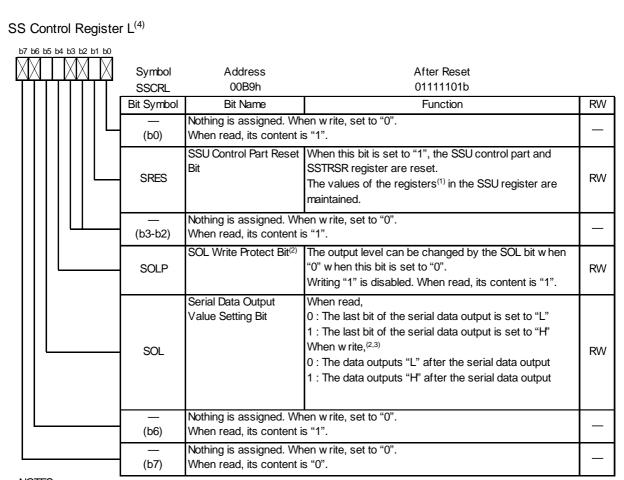

| 00B9h   | SS Control Register L                     | SSCRL | 143    |

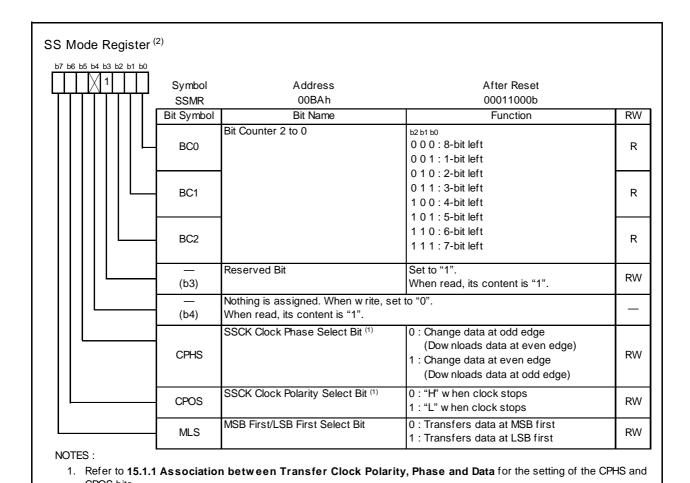

| 00BAh   | SS Mode Register                          | SSMR  | 144    |

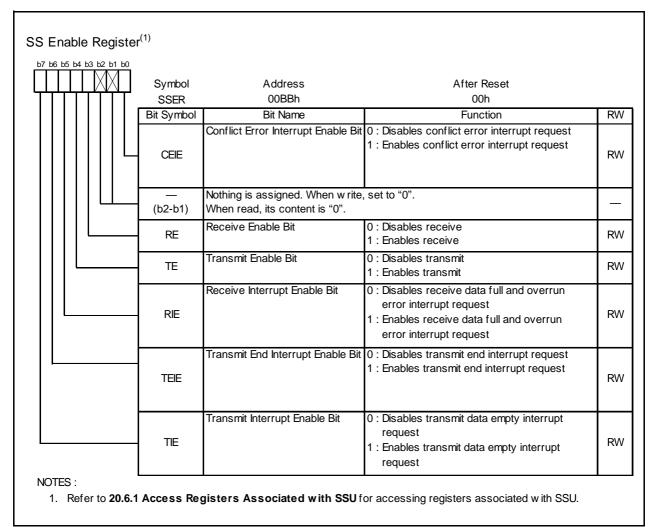

| 00BAn   | SS Enable Register                        | SSER  | 145    |

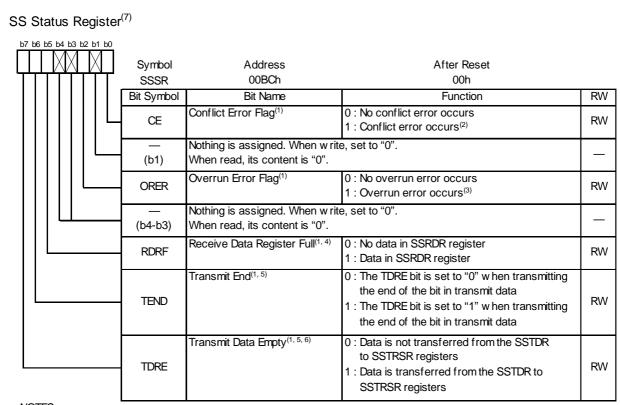

| 00BBh   | SS Status Register                        | SSSR  | 146    |

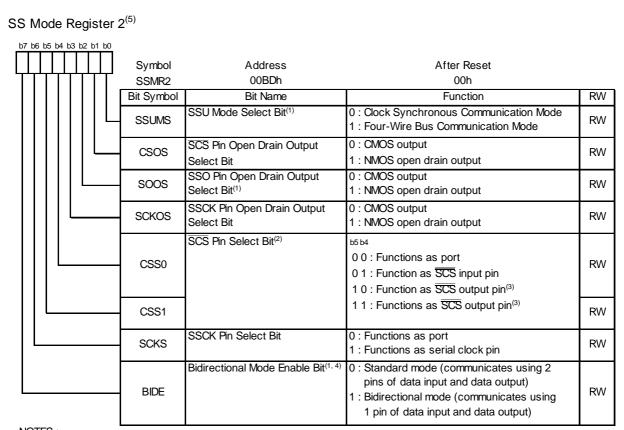

| 00BDh   | SS Mode Register 2                        | SSMR2 | 147    |

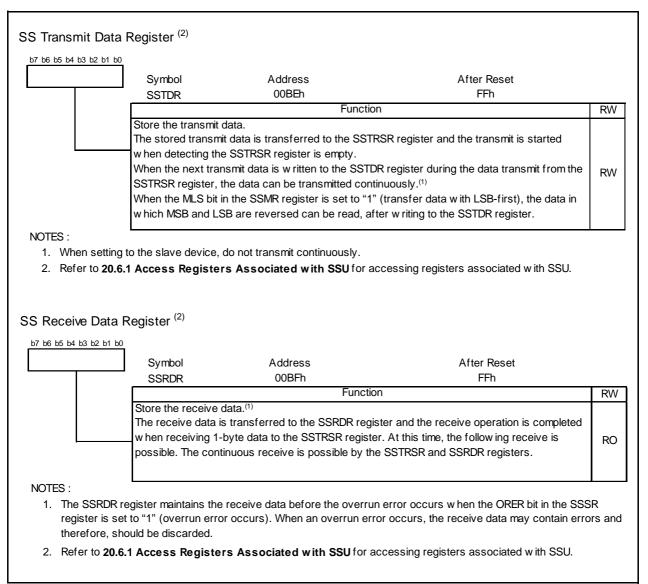

| 00BDh   | SS Transmit Data Register                 | SSTDR | 147    |

| 00BEh   | SS Receive Data Register                  | SSRDR | 148    |

|         | I OO NGCEIYE DAIA NEUISIEI                | JUNUK |        |

### NOTES:

1. Blank columns, 0100h to 01AFh and 01C0h to 02FFh are all reserved. No access is allowed.

| A alalanan       | Desistes                                | Cumahal      | Dose        |

|------------------|-----------------------------------------|--------------|-------------|

| Address<br>00C0h | Register                                | Symbol<br>AD | Page<br>171 |

| 00C0h            | A/D Register                            | AD           | 171         |

|                  |                                         |              |             |

| 00C2h            |                                         |              |             |

| 00C3h            |                                         |              |             |

| 00C4h            |                                         |              |             |

| 00C5h            |                                         |              |             |

| 00C6h            |                                         |              |             |

| 00C7h            |                                         |              |             |

| 00C8h            |                                         |              |             |

| 00C9h            |                                         |              |             |

| 00CAh            |                                         |              |             |

| 00CBh            |                                         |              |             |

| 00CCh            |                                         |              |             |

| 00CDh            |                                         |              |             |

| 00CEh            |                                         |              |             |

| 00CFh            |                                         |              |             |

| 00D0h            |                                         |              |             |

| 00D1h            |                                         |              |             |

| 00D2h            |                                         |              |             |

| 00D3h            |                                         |              |             |

| 00D3h            | A/D Control Register 2                  | ADCON2       | 171         |

| 00D4H            | 7.2 Some Region 2                       | 7.000142     | 17.         |

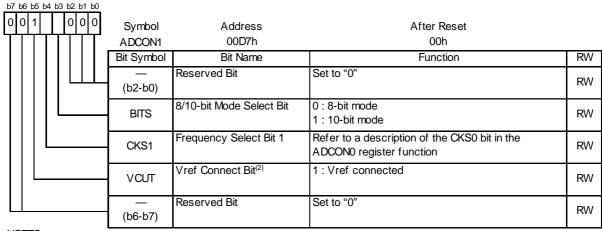

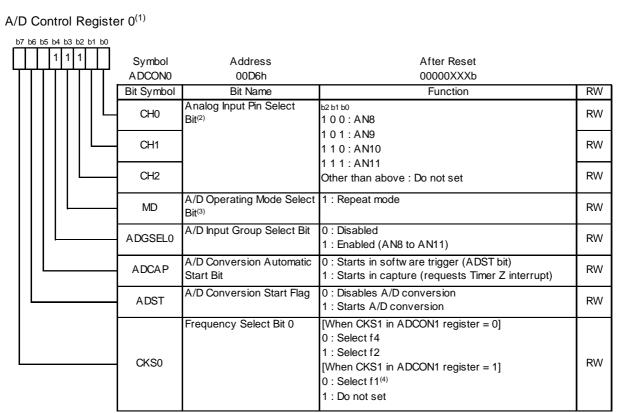

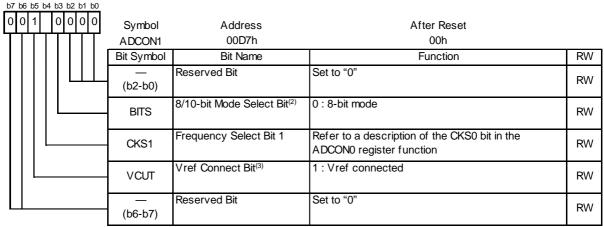

| 00D5h            | A/D Control Register 0                  | ADCON0       | 170         |

| 00D6H            | A/D Control Register 1                  | ADCON0       | 170         |

| 00D7h            | AD COULTO I VEGISTEL I                  | ADCOINT      | 170         |

|                  |                                         | +            |             |

| 00D9h            |                                         | 1            | 1           |

| 00DAh            |                                         |              | ļ           |

| 00DBh            |                                         |              |             |

| 00DCh            |                                         |              |             |

| 00DDh            |                                         |              |             |

| 00DEh            |                                         |              |             |

| 00DFh            |                                         |              |             |

| 00E0h            |                                         |              |             |

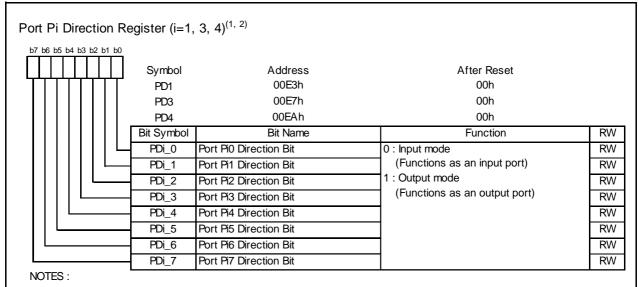

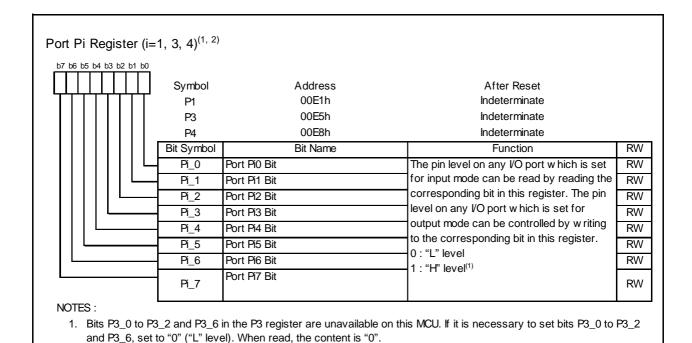

| 00E1h            | Port P1 Register                        | P1           | 184         |

| 00E2h            |                                         |              |             |

| 00E3h            | Port P1 Direction Register              | PD1          | 184         |

| 00E4h            |                                         |              |             |

| 00E5h            | Port P3 Register                        | P3           | 184         |

| 00E6h            |                                         |              |             |

| 00E7h            | Port P3 Direction Register              | PD3          | 184         |

| 00E8h            | Port P4 Register                        | P4           | 184         |

| 00E9h            | Ü                                       |              |             |

| 00EAh            | Port P4 Direction Register              | PD4          | 184         |

| 00EBh            | 3 44                                    |              | _           |

| 00ECh            |                                         |              |             |

| 00EDh            |                                         |              |             |

| 00EEh            |                                         |              |             |

| 00EFh            |                                         | +            |             |

| 00F0h            |                                         | 1            | 1           |

| 00F1h            |                                         | +            |             |

| 00F1h            |                                         | +            | 1           |

| 00F2h            |                                         | +            |             |

|                  |                                         | +            |             |

| 00F4h            |                                         | +            |             |

| 00F5h            |                                         |              | ļ           |

| 00F6h            |                                         |              | ļ           |

| 00F7h            |                                         |              | ļ           |

| 00F8h            |                                         |              |             |

| 00F9h            |                                         |              |             |

| 00FAh            |                                         |              |             |

| 00FBh            |                                         |              |             |

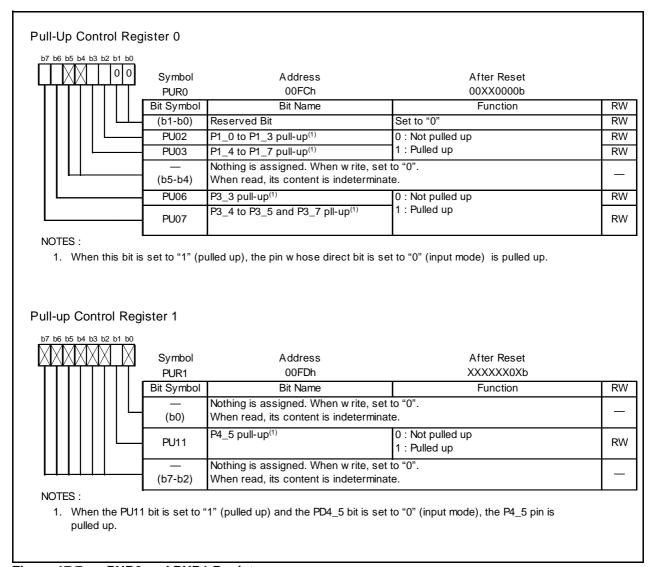

| 00FCh            | Pull-Up Control Register 0              | PUR0         | 185         |

| 00FDh            | Pull-Up Control Register 1              | PUR1         | 185         |

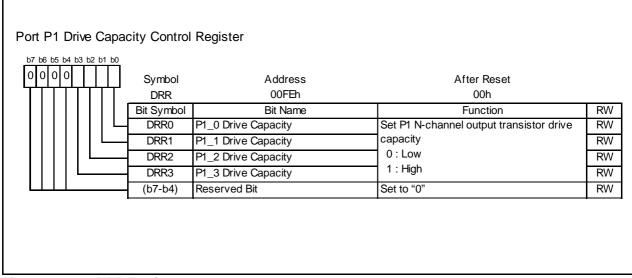

| 00FEh            | Port P1 Drive Capacity Control Register | DRR          | 185         |

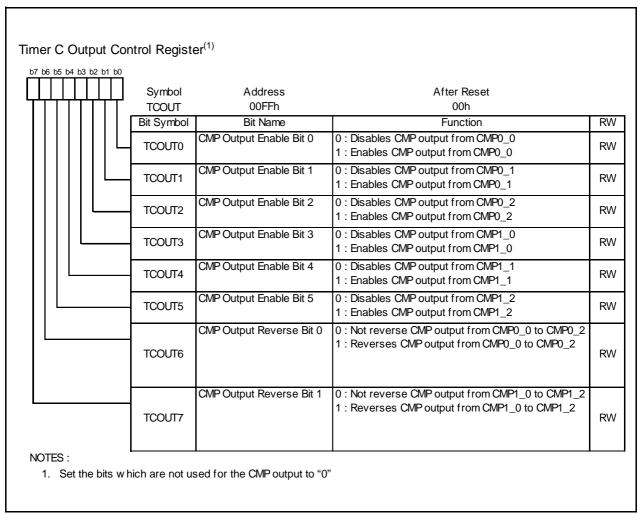

| 00FFh            | Timer C Output Control Register         | TCOUT        | 120         |

|                  |                                         |              |             |

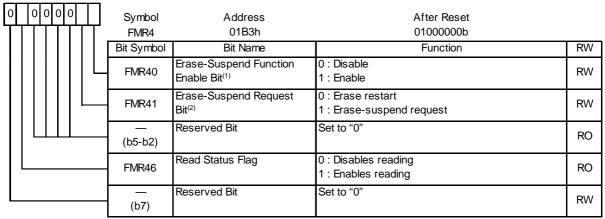

| 01B3h            | Flash Memory Control Register 4         | FMR4         | 201         |

| 01B4h            |                                         | 1            |             |

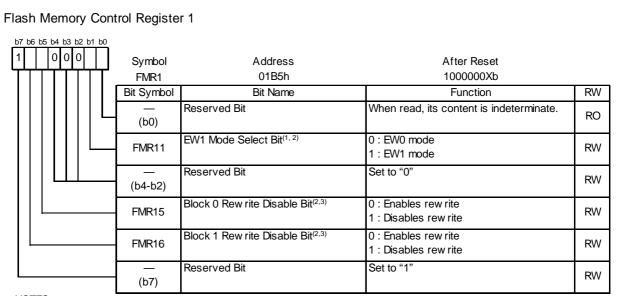

| 01B5h            | Flash Memory Control Register 1         | FMR1         | 201         |

| 01B6h            | j                                       | 1            |             |

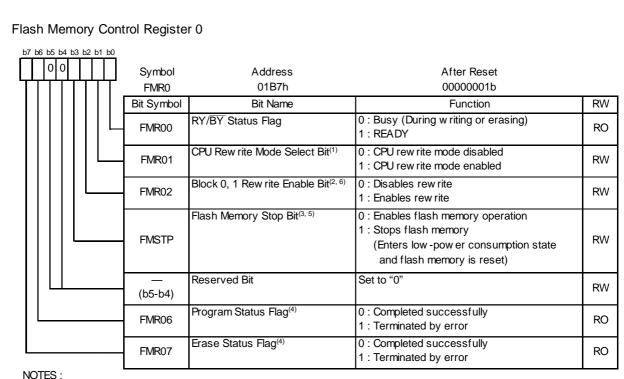

| 01B7h            | Flash Memory Control Register 0         | FMR0         | 200         |

| 1                | . · ·                                   | •            | •           |

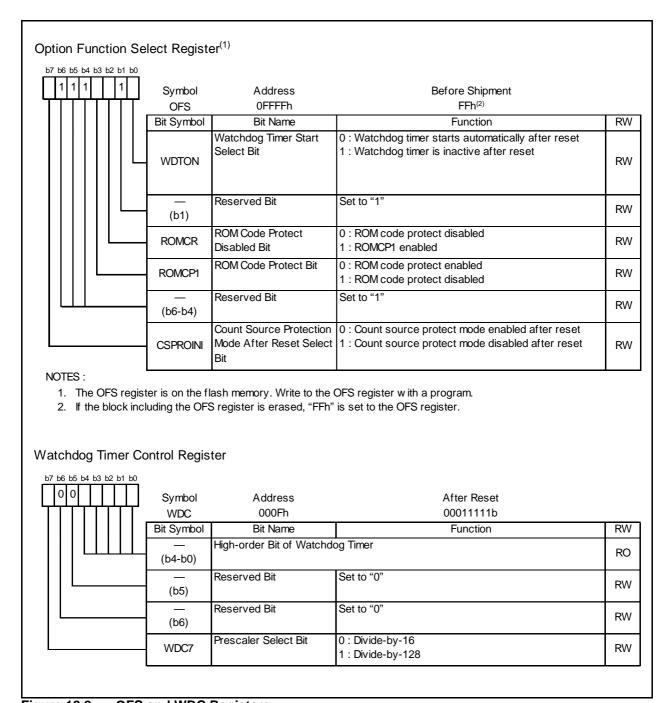

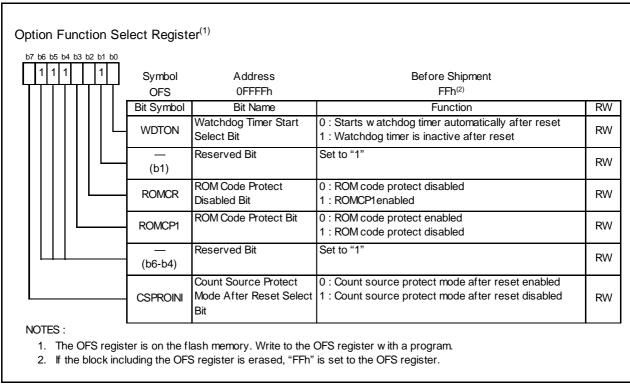

| 0FFFFh           | Optional Function Select Register       | OFS          | 79.196      |

OFFFFh

Optional Function Select Register

OFS

79,196

# R8C/14 Group, R8C/15 Group SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

REJ09B0164-0210 Rev.2.10 Jan 19, 2006

# 1. Overview

This MCU is built using the high-performance silicon gate CMOS process using a R8C/Tiny Series CPU core and is packaged in a 20-pin plastic molded LSSOP. This MCU operates using sophisticated instructions featuring a high level of instruction efficiency. With 1 Mbyte of address space, it is capable of executing instructions at high speed.

Furthermore, the data flash ROM (1KB x 2blocks) is embedded in the R8C/15 group.

The difference between R8C/14 and R8C/15 groups is only the existence of the data flash ROM. Their peripheral functions are the same.

# 1.1 Applications

Electric household appliance, office equipment, housing equipment (sensor, security), general industrial equipment, audio, etc.

# 1.2 Performance Overview

Table 1.1 lists the Performance Outline of the R8C/14 Group and Table 1.2 lists the Performance Outline of the R8C/15 Group.

Table 1.1 Performance Outline of the R8C/14 Group

|                 | Item                         | Performance                                                    |

|-----------------|------------------------------|----------------------------------------------------------------|

| CPU             | Number of Basic Instructions |                                                                |

|                 | Minimum Instruction          | 50ns(f(XIN)=20MHz, VCC=3.0 to 5.5V)                            |

|                 | Execution Time               | 100ns(f(XIN)=10MHz, VCC=2.7 to 5.5V)                           |

|                 | Operating Mode               | Single-chip                                                    |

|                 | Memory Space                 | 1 Mbyte                                                        |

|                 | Memory Capacity              | See Table 1.3 R8C/14 Group Product Information                 |

| Peripheral      | Port                         | I/O port : 13 pins (including LED drive port),                 |

| Function        |                              | Input: 2 pins                                                  |

|                 | LED Drive Port               | I/O port: 4 pins                                               |

|                 | Timer                        | Timer X: 8 bits x 1 channel, Timer Z: 8 bits x 1 channel       |

|                 |                              | (Each timer equipped with 8-bit prescaler)                     |

|                 |                              | Timer C: 16 bits × 1 channel                                   |

|                 |                              | (Circuits of input capture and output compare)                 |

|                 | Serial Interface             | 1 channel                                                      |

|                 |                              | Clock synchronous serial I/O, UART                             |

|                 | Chip-Select Clock            | 1 channel                                                      |

|                 | Synchronous Serial I/O       | T Gridinio.                                                    |

|                 | (SSU)                        |                                                                |

|                 | A/D Converter                | 10-bit A/D converter: 1 circuit, 4 channels                    |

|                 | Watchdog Timer               | 15 bits ×1 channel (with prescaler)                            |

|                 | Trateria og Timor            | Reset start selectable, Count source protection mode           |

|                 | Interrupt                    | Internal: 9 factors, External: 4 factors, Software: 4 factors, |

|                 | Interrupt                    | Priority level: 7 levels                                       |

|                 | Clock Generation Circuit     | 2 circuits                                                     |

|                 | Clock Generation Circuit     | Main clock oscillation circuit (Equipped with a built-in       |

|                 |                              | feedback resistor)                                             |

|                 |                              | On-chip oscillator (high speed, low speed)                     |

|                 |                              | , , , , , , , , , , , , , , , , , , , ,                        |

|                 |                              | Equipped with frequency adjustment function on high-           |

|                 | Oscillation Stan Datastian   | speed on-chip oscillator                                       |

|                 | Oscillation Stop Detection   | Main clock oscillation stop detection function                 |

|                 | Function                     | linali de d                                                    |

|                 | Voltage Detection Circuit    | Included                                                       |

| Floatric        | Power-On Reset Circuit       | Included                                                       |

| Electric        | Supply Voltage               | VCC=3.0 to 5.5V (f(XIN)=20MHz)                                 |

| Characteristics |                              | VCC=2.7 to 5.5V (f(XIN)=10MHz)                                 |

|                 | Power Consumption            | Typ. 9mA (VCC=5.0V, f(XIN)=20MHz)                              |

|                 |                              | Typ. 5mA (VCC=3.0V, f(XIN)=10MHz)                              |

|                 |                              | Typ. 35μA (VCC=3.0V, wait mode, peripheral clock off)          |

|                 |                              | Typ. 0.7μA (VCC=3.0V, stop mode)                               |

| Flash Memory    | Program/Erase Supply         | VCC=2.7 to 5.5V                                                |

|                 | Voltage                      |                                                                |

|                 | Program/Erase Endurance      | 100 times                                                      |

| Operating Ambi  | ient Temperature             | -20 to 85°C                                                    |

|                 |                              | -40 to 85°C (D Version)                                        |

| Package         |                              | 20-pin plastic mold LSSOP                                      |

Table 1.2 Performance Outline of the R8C/15 Group

|                 | Item                         | Performance                                                   |

|-----------------|------------------------------|---------------------------------------------------------------|

| CPU             | Number of Basic Instructions | 89 instructions                                               |

|                 | Minimum Instruction          | 50ns (f(XIN)=20MHz, VCC=3.0 to 5.5V)                          |

|                 | Execution Time               | 100ns (f(XIN)=10MHz, VCC=2.7 to 5.5V)                         |

|                 | Operating Mode               | Single-chip                                                   |

|                 | Memory Space                 | 1 Mbyte                                                       |

|                 | Memory Capacity              | See Table 1.4 R8C/15 Group Product Information                |

| Peripheral      | Port                         | I/O: 13 pins (including LED drive port),                      |

| Function        |                              | Input: 2 pins                                                 |

|                 | LED drive port               | I/O port: 4 pins                                              |

|                 | Timer                        | Timer X: 8 bits x 1 channel, Timer Z: 8 bits x 1 channel      |

|                 |                              | (Each timer equipped with 8-bit prescaler)                    |

|                 |                              | Timer C: 16 bits × 1 channel                                  |

|                 |                              | (Circuits of input capture and output compare)                |

|                 | Serial Interface             | 1 channel                                                     |

|                 | Ceriai interiace             | Clock synchronous serial I/O, UART                            |

|                 | Chip-select clock            | 1 channel                                                     |

|                 | synchronous serial I/O (SSU) |                                                               |

|                 | A/D Converter                | 10-bit A/D converter: 1 circuit, 4 channels                   |

|                 | Watchdog Timer               | 15 bits × 1 channel (with prescaler)                          |

|                 | Watchdog Timer               | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \                         |

|                 | Interrupt                    | Reset start selectable, Count source protection mode          |

|                 | Interrupt                    | Internal: 9 factors, External: 4 factors, Software: 4 factors |

|                 |                              | Priority level: 7 levels                                      |

|                 | Clock Generation Circuit     | 2 circuits                                                    |

|                 |                              | Main clock generation circuit (Equipped with a built-in       |

|                 |                              | feedback resistor)                                            |

|                 |                              | On-chip oscillator (high speed, low speed)                    |

|                 |                              | Equipped with frequency adjustment function on high-          |

|                 |                              | speed on-chip oscillator                                      |

|                 | Oscillation Stop Detection   | Main clock oscillation stop detection function                |

|                 | Function                     |                                                               |

|                 | Voltage Detection Circuit    | Included                                                      |

|                 | Power on Reset Circuit       | Included                                                      |

| Electric        | Supply Voltage               | VCC=3.0 to 5.5V (f(XIN)=20MHz)                                |

| Characteristics |                              | VCC=2.7 to 5.5V (f(XIN)=10MHz)                                |

|                 | Power Consumption            | Typ. 9mA (VCC=5.0V, f(XIN)=20MHz)                             |

|                 | ·                            | Typ. 5mA (VCC=3.0V, f(XIN)=10MHz)                             |

|                 |                              | Typ. 35μA (VCC=3.0V, wait mode, peripheral clock off)         |

|                 |                              | Typ. $0.7\mu\text{A}$ (VCC=3.0V, stop mode)                   |

| Flash Memory    | Program/Erase Supply         | VCC=2.7 to 5.5V                                               |

| i lasii womony  | Voltage                      | V00-2.7 to 0.0 V                                              |

|                 | Program/Erase Endurance      | 10,000 times (Data flash)                                     |

|                 | Togram/Liase Lindulation     | 1,000 times (Pagram ROM)                                      |

| Operating Ambi  | lent Temperature             | -20 to 85°C                                                   |

|                 | on remperature               |                                                               |

| Dackage         |                              | -40 to 85°C (D Version)                                       |

| Package         |                              | 20-pin plastic mold LSSOP                                     |

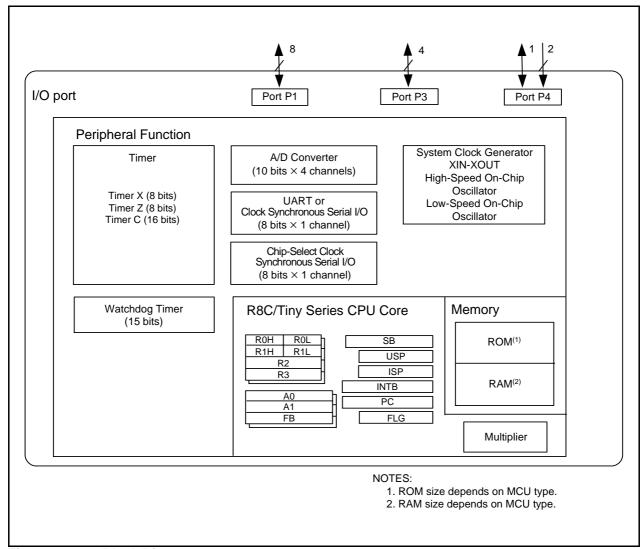

# 1.3 Block Diagram

Figure 1.1 shows a Block Diagram.

Figure 1.1 Block Diagram

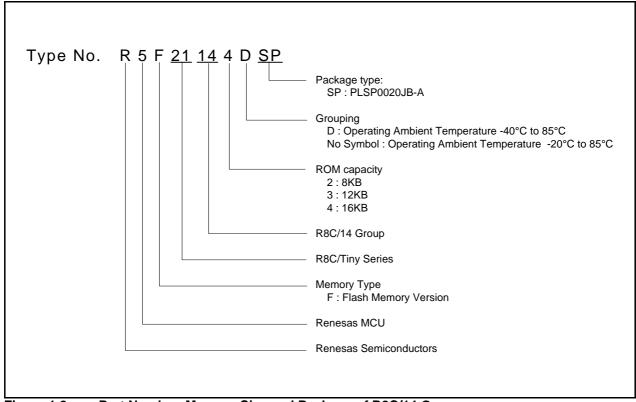

# 1.4 Product Information

Table 1.3 lists the Product Information of R8C/14 Group and Table 1.4 lists the Product Information of R8C/15 Group.

Table 1.3 Product Information of R8C/14 Group

As of Jan 2006

| Type No.    | ROM capacity | RAM capacity | Package type | Remarks              |

|-------------|--------------|--------------|--------------|----------------------|

| R5F21142SP  | 8 Kbytes     | 512 bytes    | PLSP0020JB-A | Flash memory version |

| R5F21143SP  | 12 Kbytes    | 768 bytes    | PLSP0020JB-A |                      |

| R5F21144SP  | 16 Kbytes    | 1 Kbyte      | PLSP0020JB-A |                      |

| R5F21142DSP | 8 Kbytes     | 512 bytes    | PLSP0020JB-A | D version            |

| R5F21143DSP | 12 Kbytes    | 768 bytes    | PLSP0020JB-A |                      |

| R5F21144DSP | 16 Kbytes    | 1 Kbyte      | PLSP0020JB-A |                      |

Figure 1.2 Part Number, Memory Size and Package of R8C/14 Group

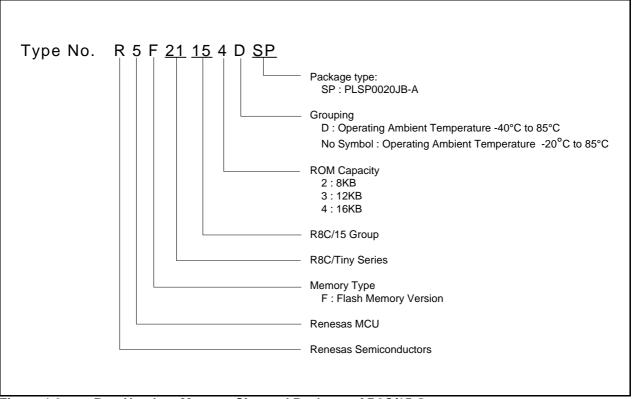

Table 1.4 Product Information of R8C/15 Group

# As of Jan 2006

| Type No.    | ROM ca      | pacity      | RAM       | Package type  | age type Remarks     |  |

|-------------|-------------|-------------|-----------|---------------|----------------------|--|

| Type No.    | Program ROM | Data flash  | capacity  | r ackage type | Remarks              |  |

| R5F21152SP  | 8 Kbytes    | 1 Kbyte x 2 | 512 bytes | PLSP0020JB-A  | Flash memory version |  |

| R5F21153SP  | 12 Kbytes   | 1 Kbyte × 2 | 768 bytes | PLSP0020JB-A  |                      |  |

| R5F21154SP  | 16 Kbytes   | 1 Kbyte × 2 | 1 Kbyte   | PLSP0020JB-A  |                      |  |

| R5F21152DSP | 8 Kbytes    | 1 Kbyte × 2 | 512 bytes | PLSP0020JB-A  | D version            |  |

| R5F21153DSP | 12 Kbytes   | 1 Kbyte x 2 | 768 bytes | PLSP0020JB-A  |                      |  |

| R5F21154DSP | 16 Kbytes   | 1 Kbyte × 2 | 1 Kbyte   | PLSP0020JB-A  |                      |  |

Figure 1.3 Part Number, Memory Size and Package of R8C/15 Group

# 1.5 Pin Assignments

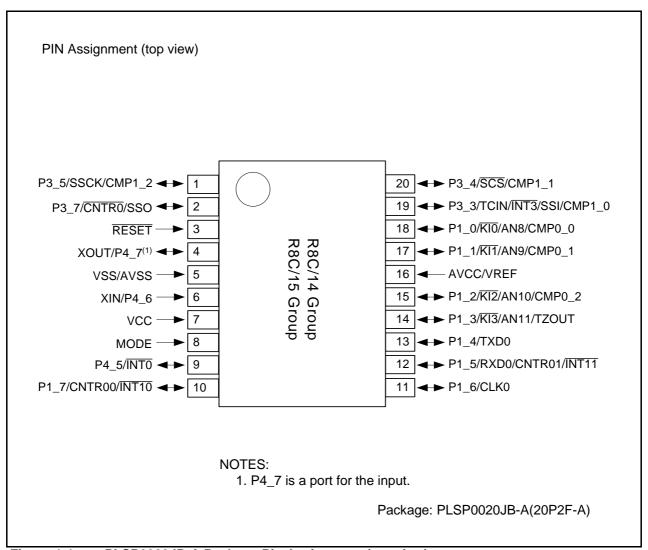

Figure 1.4 shows the PLSP0020JB-A Package Pin Assignment (top view).

Figure 1.4 PLSP0020JB-A Package Pin Assignment (top view)

Page 7 of 253

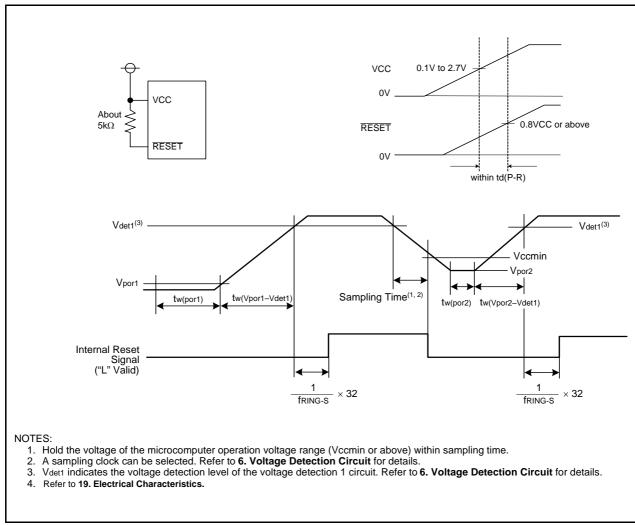

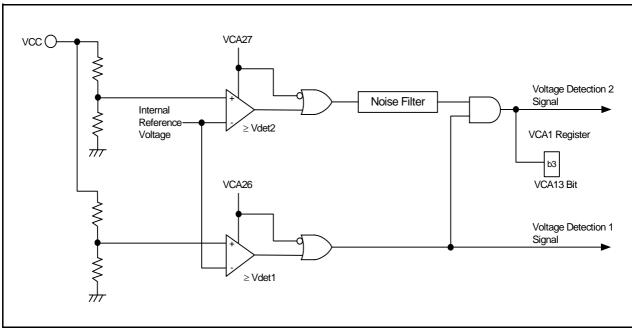

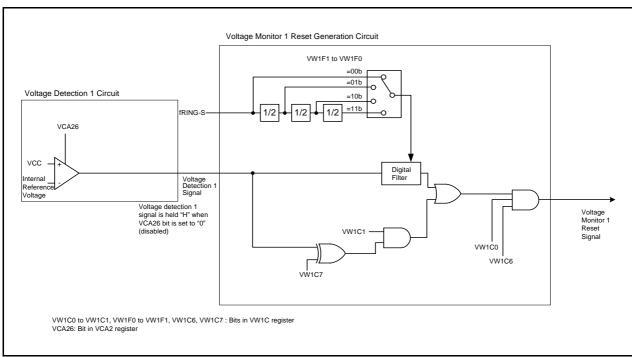

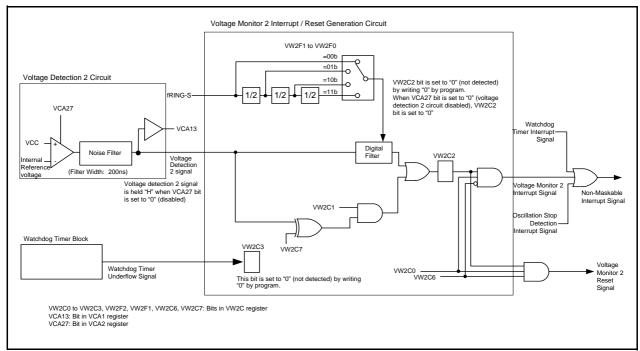

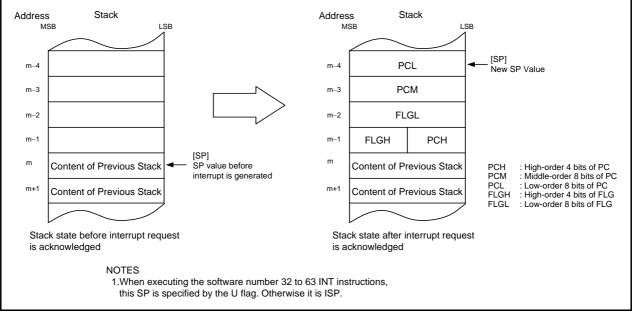

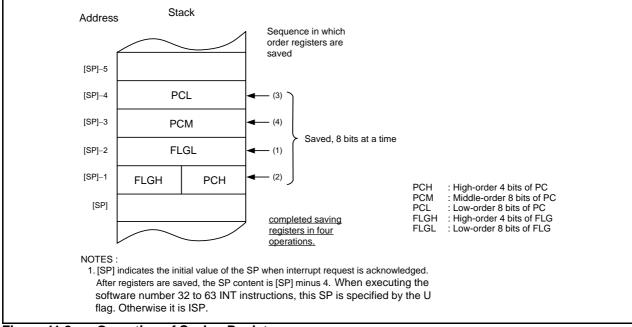

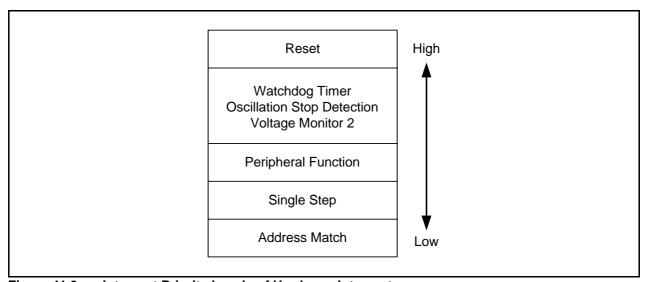

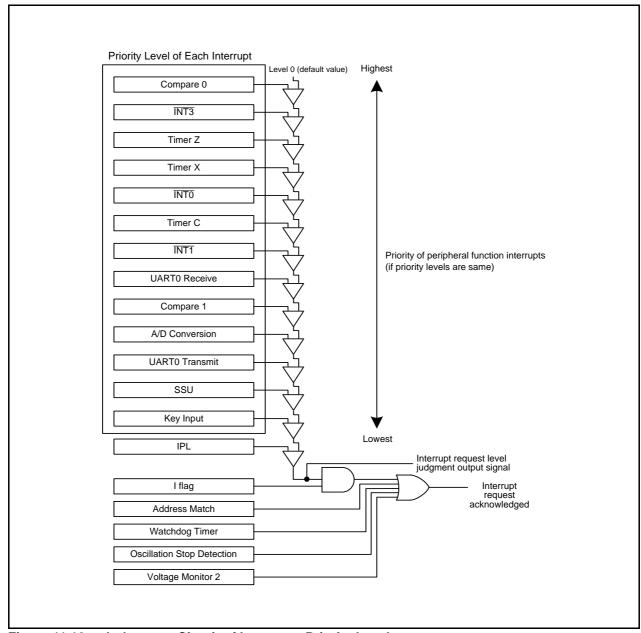

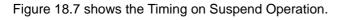

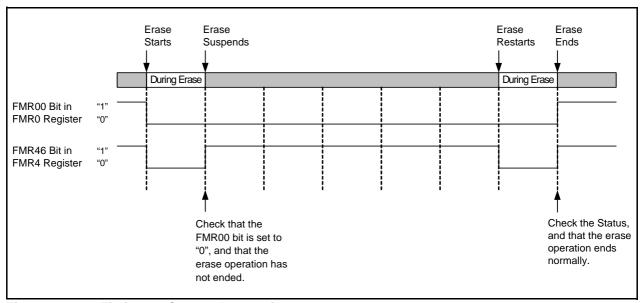

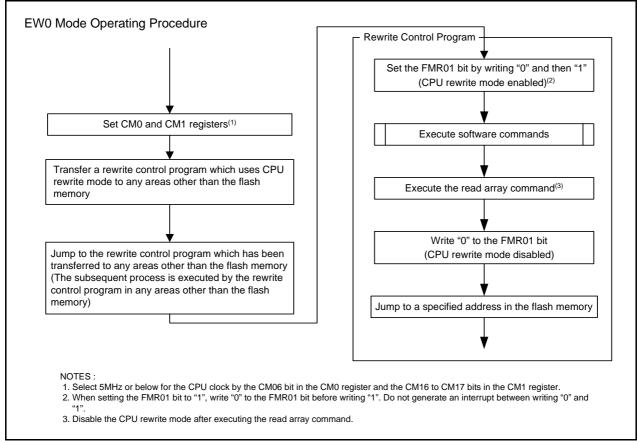

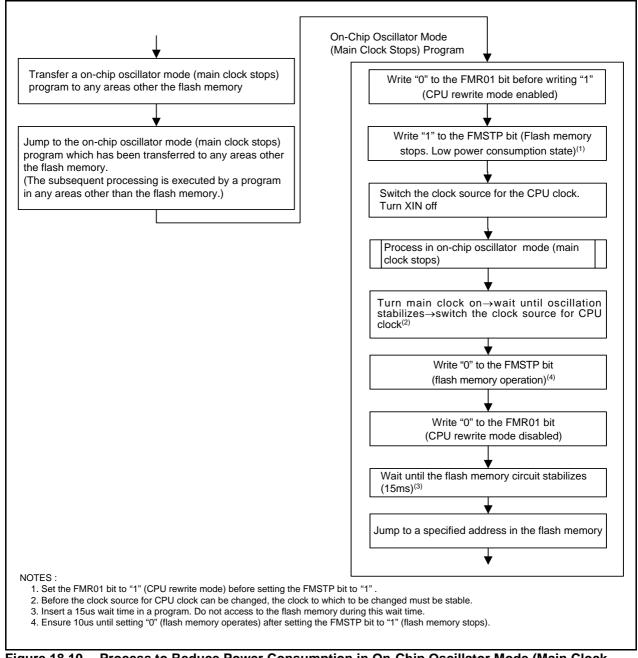

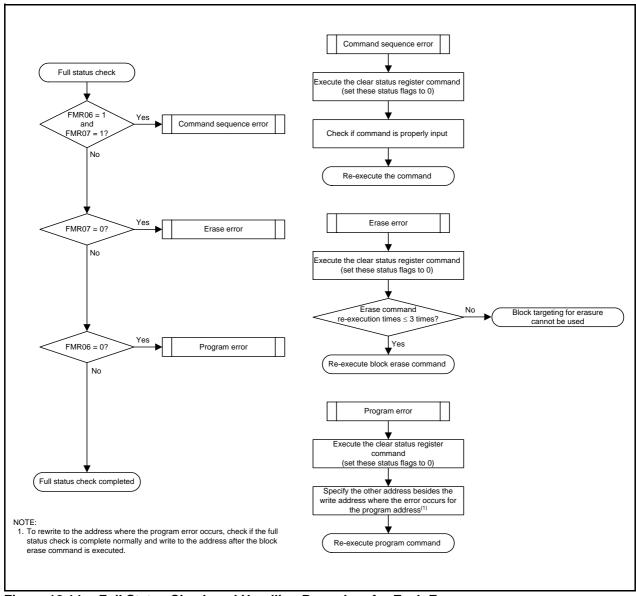

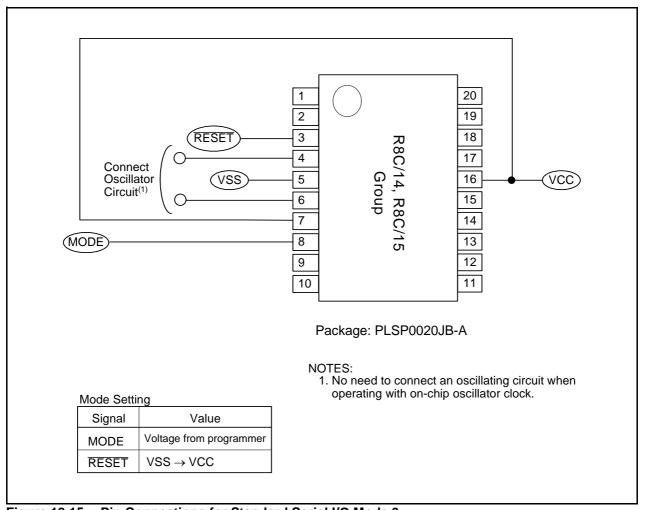

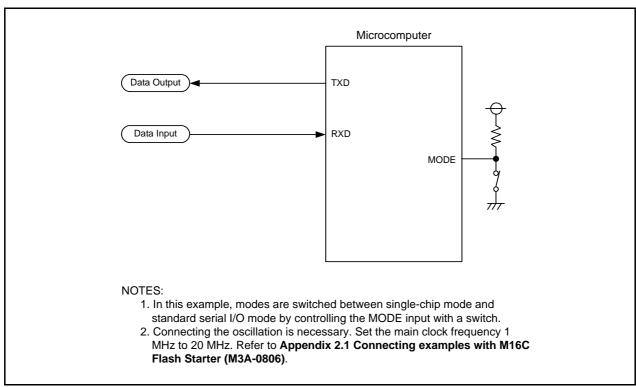

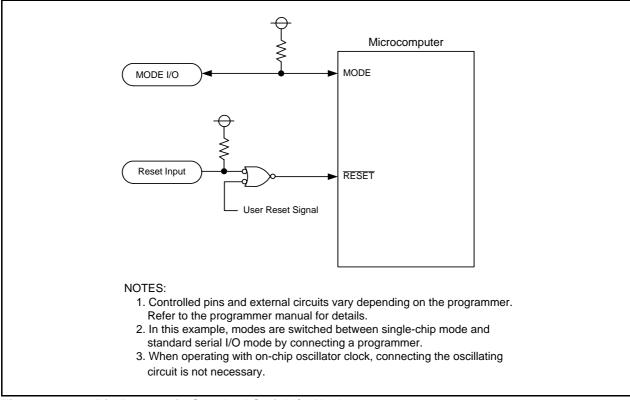

# 1.6 Pin Description